1 系统级设计与验证简介

片上电子系统的速度和复杂度的不断提高不仅使得底层的设计实现易于出问题,而且顶层的系统架构、通讯机制、软硬件划分等都可能使系统的功能、性能或成本、开发周期等指标不满足要求。一旦在底层的实现阶段发现了这种顶层的设计问题,会有大量的设计工作重新进行;此外,工程师对设计规格的理解偏差,或设计规格本身的不完整及二义性也是造成设计错误的原因之一;底层硬件的设计在验证时需要大量的输入激励和检验响应,在信号级完成这样的工作不但速度很慢而且容易遗漏。

由于电子系统中相当部分的工作是由软件完成,所以必须确保在应用环境下软硬件能够正确地协同工作。以前软件中依赖于硬件的部分通常要等到样机加工好后才能调试,使得嵌入式软件的完整验证只能在系统设计周期的后端进行,此时发现的设计错误通常要花费较高的修改代价,特别是那些牵涉到软硬件划分等系统层次的问题。

所有这些都要求我们用跟以往大不相同的方式看待电子系统的设计流程:设计规格必须用形式化的、语法严格且语义明确的高级语言描述;从系统的顶层到底层的每一适当的抽象层次都采用合适的高级语言建立相应的模型;每一层次的模型都要进行验证,并可作为下一层次系统模型的参考模型和子模块的测试平台。如此,便可形成一系列可执行的设计规格( Executable SpecifICation ),并将验证工作左移到系统设计的早期阶段,从而达到消除设计规格的歧义性和及早发现较高层次的设计错误的目的。

目前国际上已普遍做到用高级语言来进行系统的规格描述和底层实现,从而形成从系统顶层到底层的一系列可验证的模型;软件与硬件的相互验证不必等到实物样机加工好再进行,而是与硬件的RTL模型联合仿真。其存在的主要问题有:顶层设计如算法等用的是传统的软件高级语言C++、Fortran等,而底层的硬件设计用的是硬件描述语言VHDL、Verilog,这样造成整个设计和验证流程不够顺畅,各层次之间难以做到无缝连接;对于更复杂或运算量非常大的系统,验证的速度尤其是软硬件联合仿真的速度太慢,难以进行有效的验证。上述问题的解决方法是:规定软硬件设计和验证统一的高级描述语言;规范抽象方式和级别,特别是在RTL之上规范硬件平台的 建模 方法。

国际上 EDA 界经过几年的发展与讨论,公认最有前途成为电子系统设计与验证统一语言的就是 SystEMC ,它是在C++的基础上加上一套适合于硬件描述的模板库和仿真内核构成,并不断地扩充进有望成为标准的附加库,如验证库SCV、事务级建模库TLM API等。

在基于SystEMC的系统级建模和验证流程中,首先在顶层建立较高抽象级的模型,主要用于完成系统控制与算法的设计分析,进行物理架构的功能性能的设计分析。通过建立系统级的抽象模型,执行仿真分析和评估给出量化的指标,从而对系统级的功能性能作出正确的设计,并在此基础上进行软硬件模块划分。

2 模型层次

为便于后面叙述的方便,这里先简要介绍一下系统建模的几种抽象方式和应用类型。

抽象方式可分为:

应用类型可分为:

3 事务级 建模 方法TLM

事务级建模方法TLM(Transaction Level Modeling)是为了解决以下问题而发展起来的,这些问题包括提供软件开发的早期平台;系统架构探索与验证;系统级模型在模块级验证中的应用。它用于建模可执行的平台,通常只描述硬件。

所谓事务,一方面指把低层次的信息传输组合成的较高级别的传输,比如把读写一大块数据作为一个事务,它包含总线上的若干次突发传输,每个突发传输又会包含地址连续的多个数据传输;另一方面指不牵涉具体的信号,而是把传输中涉及到的信息分类作为整体表示。事务级建模方法把模块的功能和模块间的通讯分开建模,模块间通讯用事务来表示,接口用不含管脚细节的TF方式,功能也用TF方式,是否周期精确根据需要而定。通过提高抽象级别,并把分散在各模块中的通讯协议处理功能集成在专门的通讯模块中完成,极大地加快了系统仿真的速度。

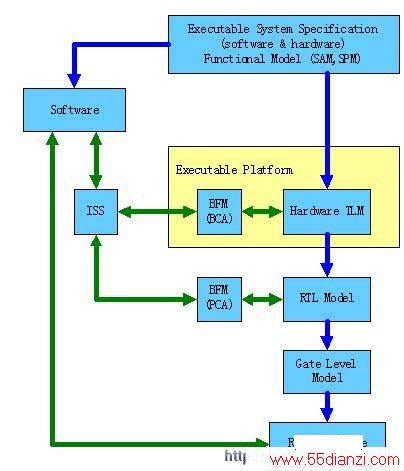

软件工程师可以使用处理器指令集仿真器ISS(Instruction Set Simulator)来测试程序,ISS使用总线事务访问外部设备,总线事务通过总线功能模型连接到硬件模型,从而使软硬件测试过程无缝连接。以前的总线功能模型是PCA,相应的硬件模型是RTL,导致仿真速度很慢, 现在通过使用事务作为内部模块间通信的方式,总线功能模型是BCA,相应的硬件模型是TLM,软件模型、硬件模型和测试平台可以在较高的抽象级连接成整体,仿真速度快100倍以上,并可在设计周期中更早的阶段与ISS一起作为软件运行的平台。具体可见示意图1。

在TLM级实现可执行的规格有助于进行系统架构的性能分析,探索不同的架构方案;为RTL设计提供参考模型和验证平台;可以作为软件开发的平台,优化软硬件划分方案。所以事务级的系统硬件可执行规格又称为可执行平台EP( Executable Platform )。它是架构精确的,为软件开发和模块级的验证提供一个快速全功能的环境。当EP作为底层RTL模块的测试平台时,需要将相应的TLM模块替换为目标RTL模块与transactor的组合,transactor是 SystEMC 的术语,作用是将一种抽象级的接口转换为另一种抽象级的接口。

图1 由TLM构成的可执行平台

由于高层模型(如算法模型)的仿真速度通常要比低一层的模型快10倍或更多,同时高层模型可重用为低层次设计的参考模型,高层的可执行规格可作为低层设计模块的验证平台,因此经常需要将不同层次的模型混合仿真。把高层模型的对外接口用transactor形式转换成低层模型的接口,就可以连接到整个系统上。

4 总结

系统级设计和验证包括从系统规格开始的设计输入、架构评估、功能验证、多层次多语言混合验证、软硬件协同开发及验证等高抽象度的描述方法和验证技术。

SystEMC作为一种适用于多层次建模和仿真的高级语言,已被广泛应用于系统级设计和验证的多个领域,为研究不同的系统结构、进行算法评估、软硬件任务划分和软件开发提供了有效的方法。它能使整个团队使用一种语言来灵活地组合不同的抽象层次,使设计者优化系统的设计和验证流程。

事务级模型(TLM)与寄存器传输级(RTL)模型相比较,是在更高抽象级别上对系统硬件建模,在结构级的组件上交换数据或执行事件。事务级描述抽象度较高,比RTL容易开发,这样在设计早期就可得到系统的硬件模型;TLM比相应的RTL模型仿真速度快100倍以上,在TLM级的平台上可以很快地运行软件,非常适合于架构和性能分析、早期的软硬件协同验证。

参考文献

[1]CoWare Inc., Transaction Level Modeling and the ConvergenSC products

[2]OCPIP, SystemC based SoC CommunICation Modeling for the OCP Protocol

[3]OSCI, Transaction Level Modeling in SystemC

[4]Model Technology Inc., Utilizing SystemC for Design and Verification

[5]OCPIP, Socket-Centric IP Core Interface Maximizes IP Applications

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:语音合成芯片的ASIC设计