FPGA设计者对非易失可重复编程FPGA解决方案的喜爱仍在延续,这种方案所需的相关额外费用并不太大 。

设计人员对其的喜爱源于他们喜欢从一种产品中获取多种能力,而迄今为止,只有非易失性解决方案能够满足他们的要求,因为它可以提供:最小的电路板面积和最简单的系统集成、上电后能很快地获取逻辑,以及最高的安全性。

事实上,除了这些传统要求,在前两代 非易失FPGA 产品的经验基础上,莱迪思半导体( LattICe SEMIconductor)公司还认识到需要灵活的片上非易失存储器,以及作为非易失FPGA新要求的用于现场逻辑更新的全面解决方案。

非易失FPGA的几种方案

如今市场上有三种类型的FPGA:第一种是传统的SRAM FPGA,系统上电时需要一个外部的非易失存储器来配置FPGA;第二种是混合方法,把SRAM FPGA和非易失存储器组合在单个封装中;第三种常称为真正的单片非易失FPGA,将非易失的单元嵌入在同一裸片上作为FPGA逻辑。如图1所示,混合方法比SRAM方法好一些,而真正的非易失方法则是最佳方案,具有小尺寸、高安全性和上电时的瞬时运作。

图1 : 三种不同类型的FPGA

非易失可重复编程FPGA的应用

在诸如通信、消费、计算、军事和汽车等广泛且多样的终端市场中,非易失可重复编程FPGA被用来实现系统逻辑。非易失FPGA特别吸引那些要求减少部件数和占位面积,并迅速获得逻辑或高安全性的应用。

1 小尺寸应用

这里所说的小尺寸应用包括:手持条码扫描器、手持条码阅读器、智能电话、仪器与传感器、航空电子设备等。传统的 SRAM FPGA 需要一个引导存储器,在上电时载入SRAM配置。有时候配置载入通过电路板上的微处理器来完成,而另外一些时候应用中需要一个独立的引导存储器。这两个解决方案都不理想。从系统微处理器进行引导引入了额外的硬件和软件间的相互依赖,还要求微处理器在FPGA配置前就运行,从而阻碍了其在系统中的核心功能。使用独立的引导存储器则增加了电路板的面积、元件,及相关成本。通过整合片上的引导存储器,非易失FPGA提供了一个可选方案,也是更加完美的解决方案。

2 要求快速获得逻辑的应用

片上非易失存储器能使器件在上电1毫秒内准备好运作,与SRAM和混合FPGA相比,SRAM和混合FPGA的配置需要数十或几百毫秒。图2为“唤醒时间”的差别。在许多常见应用中,真正的非易失FPGA所带来的快速获得逻辑的功能正是人们希望得到的特性。这些应用包括:即插即用总线接口(PCI, PCI Express, CAN)、上电复位控制、处理器总线译码、FPGA加载器、ASIC初始化以及使用工作循环的低功耗设计等。

图2 具有非易失FPGA的迅速获得逻辑的能力

3 要求设计安全性的应用

在当今复杂的系统中,越来越多的FPGA被用来取代传统上用ASIC和微处理器实现的功能。十年前,FPGA只是系统的外围,而如今它是心脏。目前的FPGA工艺已使门数量达到几百万,FPGA成为非法盗版者的目标。FPGA设计者逐渐开始关注克隆、反向工程、过量生产、盗版服务等问题。

系统设计者使用的大多数SRAM FPGA需要在系统每次上电时由引导器件进行配置。引导器件和FPGA之间的连接存在很大的风险,因为配置数据暴露在外,易于在上电时被盗取。在封装中嵌入非易失存储器的混合方法对这种情况的改进有限。然而,相关的工具能够免除封装材料并获得裸片的互连。真正的单片非易失器件没有这样的互联,因此能够提供绝佳的设计安全性。

除了设计被盗取或复制,在许多系统中很重要的是确保FPGA没有被篡改。有这些要求的应用包括:信用卡读卡器、自动出纳机、武器系统以及游戏系统。

4 非易失存储应用

由于非易失FPGA在密度和功能方面的水平继续增强,许多设计者要在设计中整合非易失存储器。这些需求分成两种。

第一种是能整合小的独立的EEPROM存储器,在许多系统中存储数据,例如电子ID码、版本码、日期打印、校准设置和资产ID。这种类型的存储器不是经常通过串行接口访问的。

第二种类型是能够整合大的存储块,典型的应用为存储数据,例如错误码、上电自测试、数据查找表和微处理器码。对数据的写操作不是经常的,读数据则是经常的,读操作的速度影响整个系统的性能。

5 现场更新

当设备用于现场时,提供FPGA配置更新的能力就益发重要,如图3所示。这种能力为设备供应者提供了竞争优势,能对标准的改变、新的服务以及排除故障作出迅速回应。

图3 在现场更新逻辑

LattICe XP2器件

Lattice与富士通(Fujitsu)合作开发了90nm嵌入式闪存工艺的 LatticeXP2系列,这种工艺使LatticeXP2器件的成本减少了50%。该器件把成功用于LatticeECP2 SRAM的功能块和Flash单元组合在一起,称之为flexiFLASH。

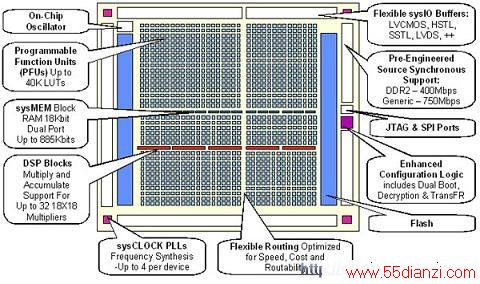

1 LatticeXP2结构-功能块

LatticeXP2器件的核心含有能够实现逻辑的可编程功能单元(PFU),以及占25%逻辑块的分布式存储器。用4输入的查找表和寄存器对来实现逻辑,对于FPGA工业、能够被系统设计者充分理解以及逻辑综合工具提供者来说,这是一个事实上的标准。分布式存储器为设计者提供了有效的方法实现便笺式存储器。这个系列提供5K到40K LUT。

嵌入式RAM(EBR)的sysMEM行提供166K -885Kb的18kb块的双口存储器。器件还有乘、加、减和累加功能的sysDSP块,用来实现通用的DSP功能,例如FIR滤波器、FFT和复杂算法。sysDSP块提供12-32的18x18乘法器。

器件的I/O引脚数从86到540,能与各种I/O标准互连,包括LVCMOS、PCI、LVTTL、LVDS和SSTL, HSTL。此外与附加 的外部电阻相配合可以模仿LVPECL、BLVDS 和RSDS接口标准。校准DQS延时块的DLL、DDR寄存器和时钟传送电路能实现达400Mbps的DDR和DDR2存储器接口。还可以与器件一起实现750Mbps的普通DDR接口。

器件还提供多达4个PLL,用于时钟综合与对齐。片上振荡器提供低精度的时钟源,适用于许多辅助功能,例如监视时钟和键盘扫描逻辑。时钟的分布为8个全局时钟、8个区域时钟,或者2个高速边沿时钟。图的左边和右边为Flash存储器块,用于器件的配置。

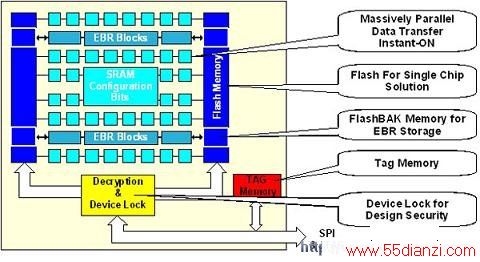

器件工作于1.2伏的内部电压并有各种可供选择的封装。图4为器件的整个结构,图5为系列中的各个成员的详情。下面将详述非易失特性的运作。

图4 LatticeXP2结构

图5 flexiFLASH结构

FlexiFLASH详情

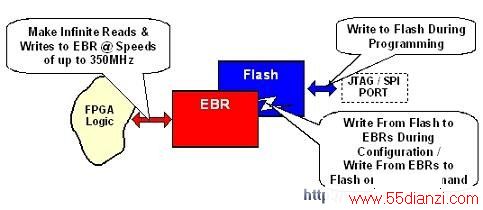

LatticeXP2器件在结构中组合了Flash 和SRAM,称为flexiFLASH。器件逻辑配置和嵌入式RAM块数据存储在SRAM单元。上电时或者根据用户命令,源于片上Flash存储器的块以并行形式载入SRAM。这种迅速的传送方式使器件具有瞬时的特性,片上的Flash存储器导致了单片解决方案。通过JTAG 或者SPI端口可以对Flash存储器进行写操作,如图5所示。

FlashBAK存储器

为了满足存储大块的数据,LatticeXP2器件提供称为FlashBAK存储器的创新功能。如前所述,上电时从片上Flash存储器装载至EBR。EBR能以350MHz的速度进行读或写。可以根据要求在FPGA内切换信号,根据当前EBR的内容,重写Flash是可能的。这个过程大约为1秒的时间。用这个方法,用户可获得高性能和无限次的读和写,这是非易失Flash存储器与SRAM相结合的结果。这个器件提供166K 和 885Kbit的 FlashBAK存储器。

图6 非易失FlashBAK存储

串行TAG存储器

为了提供小量可串行访问的存储器,每个器件都有0.6K至3.4Kbit的串行TAG存储器。如图7所示,可以通过器件的JTAG接口或者FPGA逻辑访问这个存储器。这个存储器位于器件安全结构的外面,可以独立地访问器件安全设置。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术