������ ��

���� RC6 ����ΪAES(Advanced Encryption Standard)�ĺ�ѡ�㷨�ύ��NIST(�������ұ���)��һ���µķ������롣������RC5�Ļ�������Ƶģ��Ը��õط���AES��Ҫ��������˰�ȫ�ԣ���ǿ�����ܡ�����AES��Ҫ��һ������������봦��128λ���룯������ݡ�����RC5��һ���dz���ķ������룬��������128λ�����ʱ����2��64λ�����Ĵ�������AESĿǰ�ڽ���Ч�ʺͼ��治֧��64λ����������RC6�����������ʹ��4��32λ�Ĵ���������2��64λ�Ĵ������Ը��õ�ʵ�� �ӽ��� ������ FPGA ��ʵ��RC6�㷨��������������ٶȡ�оƬ���ΪRC6�㷨�������������������������ɼӽ��ܲ��������Է����ʵ�ֶԼӽ��ܵķ������о�����ˣ���оƬ������Ϊ Э������ ��������

����1 RC6�㷨

����1.1 RC6�㷨����

����RC6������RC5��Ƽ��㷺ʹ��������ص�ѭ����λ˼�룬ͬʱ��ǿ�˵ֿ��������������Ľ���RC5��ѭ����λ��λ���������ڼĴ���������λ�IJ��㡣RC6�µ���ɫ�������������ԭ��2��������չΪ4�������������㷽������ʹ���������˷����������˷���ʹ������ÿһ������غ�����������ɢ(diffusion)����Ϊ������ʹ�ü�ʹ���ٵĻغ���Ҳ�кܸߵİ�ȫ�ԡ�ͬʱ��RC6�����õIJ��������ڴִ������ϸ�Ч�ʵ�ʵ�֣�����˼����ٶȡ�RC6��һ�ְ�ȫ���ܹ��������Ҽ�������ܷ������ṩ�˽ϺõIJ��Խ���Ͳ��������൱��ĵ��ԡ�RC6���Եֿ�������֪�Ĺ������ܹ��ṩAES��Ҫ��İ�ȫ�ԣ�����˵�ǽ��������൱�����һ�ּ��ܷ���

����RC6����ʹ��2��64λ�����Ĵ�����������4��32λ�Ĵ��������ʹ����ÿ��ѭ����Ҫ����2��ѭ����λ�������ø��������λ������ѭ��������RC6�����ķֱ����4������A��B��C��D���տ�ʼ�ֱ�������ĵij�ʼֵ�������������Ϊ4�����ĵ����ֵ��

����1��2 RC6�Ĺ���ԭ��

����RC6�Dz��������ķ����㷨��ʵ��������3������ȷ����һ�������㷨�塣һ���ض���RC6���Ա�ʾΪRC6һw��r��b��3������w��r��b�ֱ�Ϊ�ֳ���ѭ����������Կ���ȡ�AES�У�w=32��r=20��������У���Կ����bΪ128λ(16�ֽ�)��RC6��4��wλ�ļĴ���A��B��C��D�������������ĺ���������ġ����ĺ����ĵĵ�һ���ֽڴ����A������ֽڣ������ӽ��ܺõ������ĺ����ĵ����һ���ֽڴ����D������ֽڡ�

����1��2��1 RC6һw��r��b��������

�����������㹲������6�֣���ģ2w�������㣬��ʾΪ��+������ģ2w�������㣬��ʾΪ��һ��������λ������㣬��ʾΪ����������ѭ�����ƣ���aѭ������bλ��ʾΪ��a<<<b������ѭ�����ƣ���aѭ������bλ��ʾΪ��a>>>b������ģ2w�˷�����ʾΪ��������

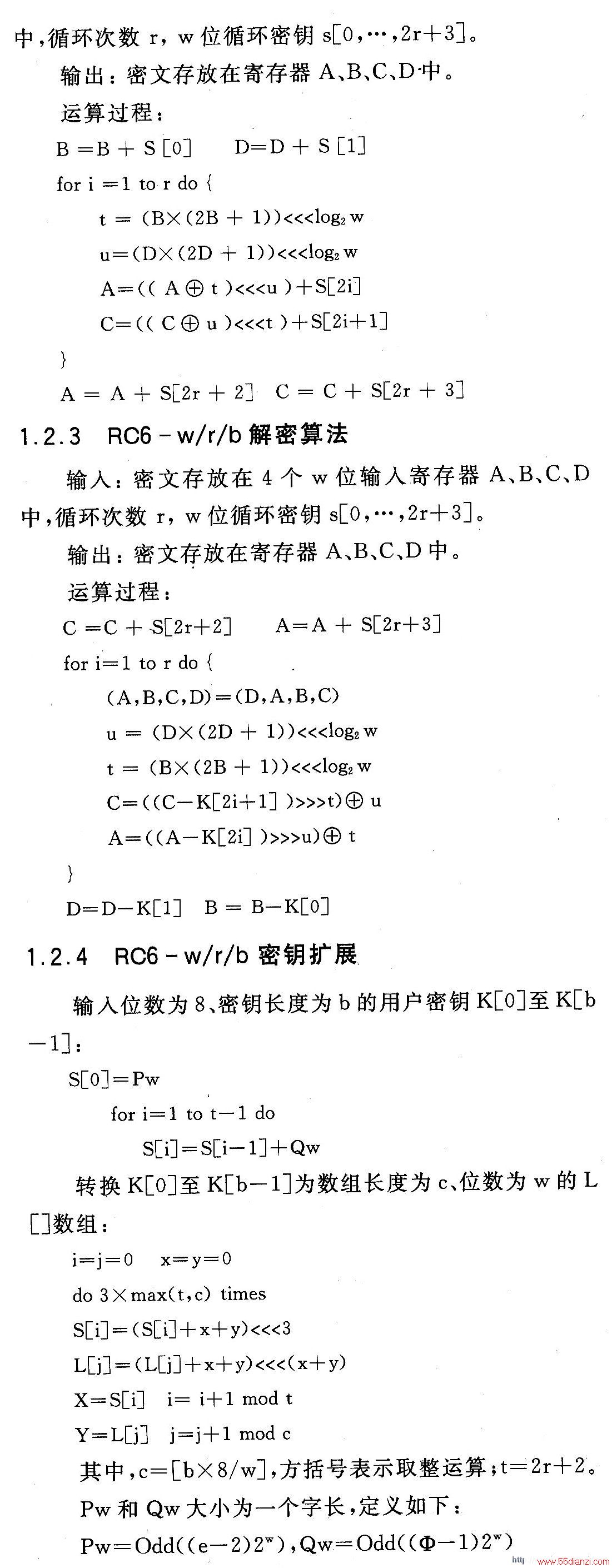

����1��2��2 RC6һw��r��b�����㷨

�������룺���Ĵ����4��wλ����Ĵ���A��B��C��D

�����ԭͼ

����ʽ�У�eһ2��782 818 284 59��(��Ȼ����);��=1��618 033 988 749��(�ƽ�ָ�)

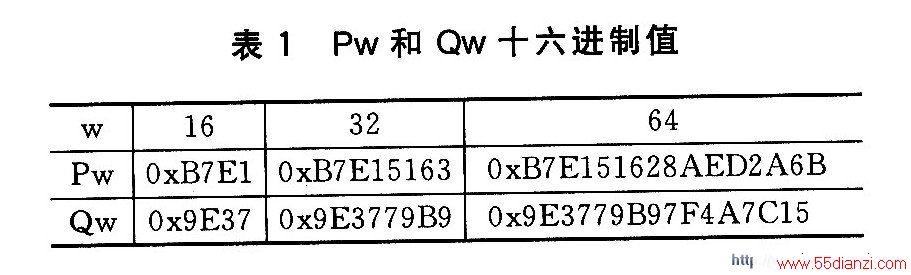

������w�ֱ�Ϊ16��32��64ʱ������Pw��Qw�ֱ����1���С��ڱ�����У�w=16������Ϊ128λ������Կ���õ�����44��32λ����Կ��

�����ԭͼ

����2 RC6�ӽ����㷨Э���������

����2��1 RC6Э�������Ķ���ṹ���

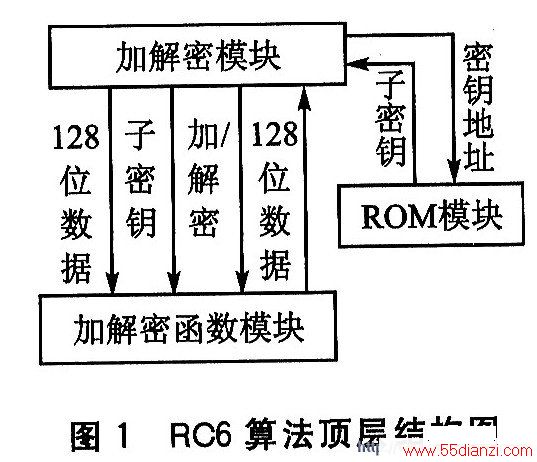

����RC6Э��������������3��ģ�飺�ӽ���ģ�飬�ӽ��ܺ���ģ���ROMģ�顣����ṹ��ͼ1��ʾ��

�����ӽ���ģ�飺���������������ӣ�����ѡ��״̬�����Լ���������������ROM����ȡַ����������128λ���Ļ����ģ���������һ��״̬���������˳��ִ�кͱ�֤ѭ�����ƣ�ʵ�ֶ�ROM��44������Կ��ȡ���Լ����������뺯���н��д�������������ROM�ĵ�ַ����һ��ʱ�ӿ����£�����Կ���ݵ������һ������ʱ����������һ�����Ʊ���cntʵ�ֵ�ַ��ǰһ��ʱ����������ROM��ROM���յ����������Կ��ʹ�ڽ������ݼӽ��ܴ���ʱ���Ѿ������õ�����Կ���á�

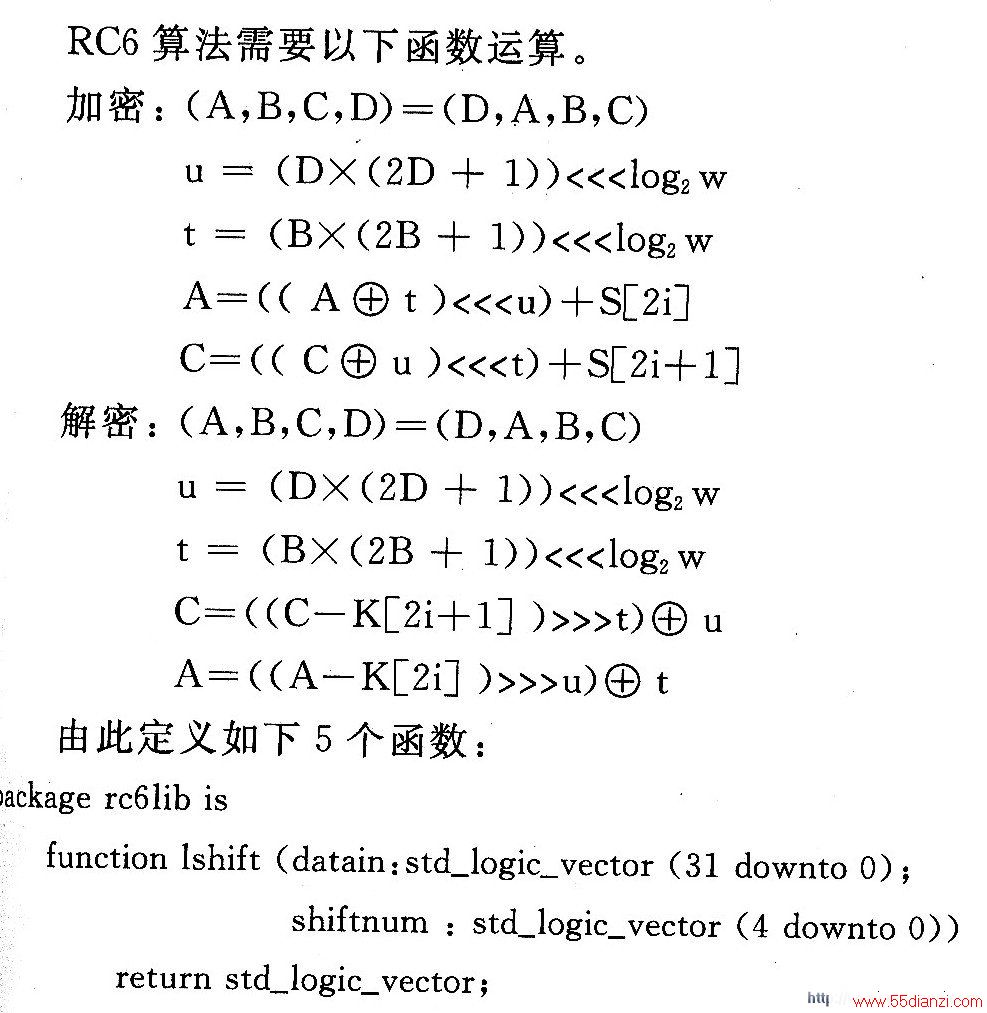

�����ӽ��ܺ���ģ�飺����work�û��Զ��庯���⣬�����㷨���õ��ĺ��������а���5���������ֱ��ǣ�rfunct��afunct��cfunct��lshift��rshift�������ļ�ѭ�����ô˺���21�Σ����мӽ������㡣

����ROMģ�飺����QUARTusII���潫Ԥ���������Կ����rc6keyrom��mif�ļ��У�����QuartusII��MegaWizardPlug��In Manager���Զ�����ROM���������ļ����á���Ҫ��ǰ����QuartusII����һ����mif�ļ���������Կ���������롣

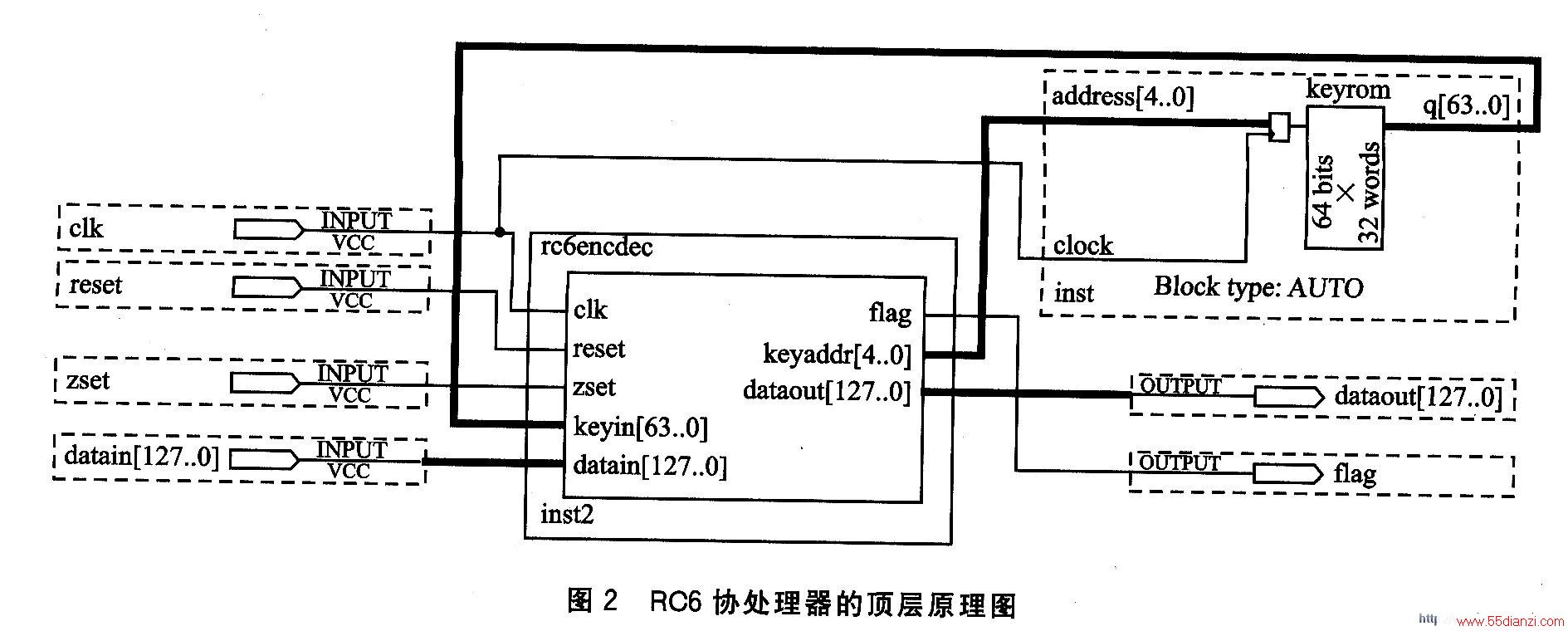

����2��2 RC6 Э������ �Ķ���ԭ��ͼ

������ͼ2��ʾ������ FPGA ��RC6�㷨Э��������3��ģ�飺����ģ�顢RC6 �ӽ��� ����ģ���ROMģ�顣����260��I��0�ڣ�����131����˿ں�129������˿ڡ�

�����ԭͼ

����2��3 ��ģ��Ĺ��ܼ�ʵ��

����2��3��1 ROMģ��

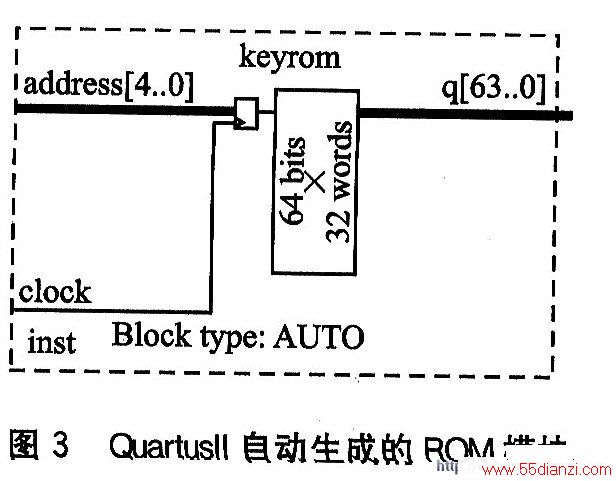

����ͼ3ΪQUARTusII�Զ����ɵ�ROMģ�顣ROMȡַ��Ҫ�ɼӽ���ģ���ṩ��ַ���룬Ȼ���������Կ�������ַΪaddress[4����0]�����Ϊq[63����0]��������Կһ��������������н��С�

�����ԭͼ

����ROMģ���������ַ�͵õ�����Կ����֮�䣬��һ������ʱ���ӵ�ַ��00�����룬��ʼ��ȡ���������Կ��ʱ��Լһ��ʱ���������ҡ�����������������ROMʱ������ǰ1��2��ʱ�������ַ��

�����ԭͼ

����������5�������ͼӽ��ܿ����źţ�����ʵ�ִ��㷨��һ�μ��㡣����������Ҫ���м����128λ����da��tain��2������Կkeyl��key2���Լ��ӽ��ܿ����ź����뵽rfunct���������rfunct������䵽a��b��c��d�ĸ��Ĵ���������b=(b+b+1)��b��d=(d+d+1)��d��Ȼ��������ƺ�������templ=b<<<5��temp2=d<<<5������afunct��cfunct����a��c��������a��b��c��dΪdataout��������������dataout��

����2��3��3 �ӽ��ܿ���ģ��

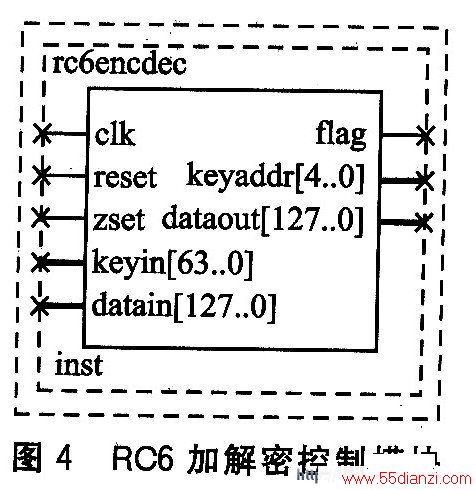

������ͼ4��ʾ��RC6�ӽ��ܶ˿ڶ���Ϊ��

��������˿�

��������˿�

����ģ�鹦��

������ROMģ���У����հ���2������Կ������keyin������ǰ32λ�ͺ�32λ�ֱ�Ϊһ��32λ����Կ������zset�źŶ���Կ�����ݽ��мӽ��ܲ�����

������������������һ��״̬����ʵ�ּӽ������㣺��1��״̬�������ݵij�����������128λ���ݷֳ�4��32λ���ݱ�����a��b��c��d��4���Ĵ����У���2��״̬�������ݵij������㣬�����������128λ�Ĵ���data�У���3��״̬�͵�4��״̬����ѭ��������ROM����20�ν�����һ�߽���ROM����Կ���ݣ�һ�߶�data�������㣬���һ��״̬���������2����Կ���������ļӽ������㣬�õ��µ�a��b��c��d��������ϳɼӣ����ܺ�����ݣ����������

���Ĺؼ��֣�������ϵ��ʽDSP/FPGA��������Ƭ��-�����豸 - DSP/FPGA����