2.3.4 加解密顶层模块

RC6加解密算法的顶层模块包括了加解密控制模块和ROM模块。输入/输出信号描述如下:

输入信号

输出信号

此加解密模块需要260个I/0端口,如果加入串口通信,可将128位的输入信号和输出信号分别利用l位的输入端口和1位的输出端口来实现数据传输,非常方便。

2.4 仿真结果分析

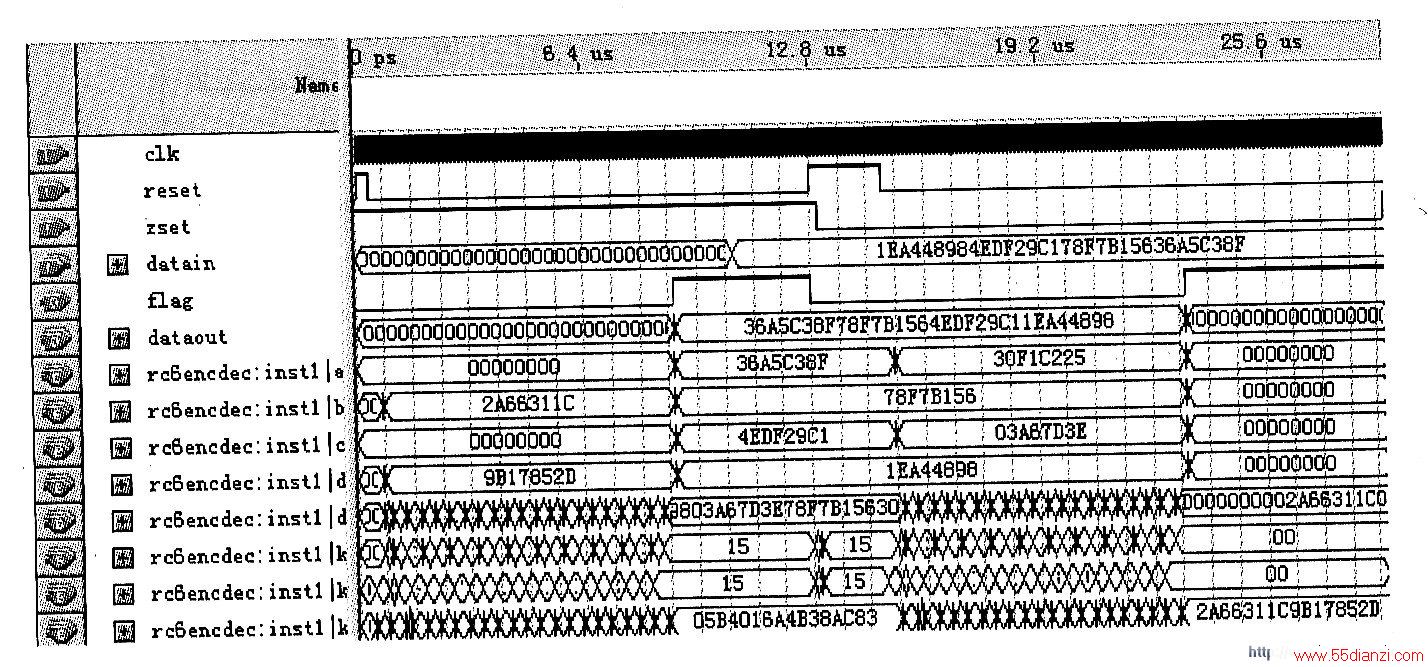

图5为RC6加解密算法的功能仿真图,输入和输出是128位。当输入明文为128位全零数据时,得到的加密结果是36A5C38F78F781564EDF29C11EA44898,解密结果是全零。另外,还测试了其他的一些数据,根据官方公布的标准,此加解密模块功能正确。

在进行仿真时,RC6加解密模块工作时钟周期为100ns,频率为10 MHz。从reset低电平开始后的第一个时钟上升沿(0.45μs),至加解密运算结束并输出结束信号flag(上升沿,8.958 376μs),总共耗时约为8.5μs。

点击看原图

图5 RC6加解密算法功能仿真图

结 语

本文基于FPGA技术,实现了RC6算法。整个设计包括加解密函数模块、加解密控制模块、ROM模块、UART模块、输入/输出控制模块等,通过软件的仿真,并将程序下载到FPGA芯片进行硬件调试,验证了设计的正确性和有效性。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术