1、引言

随着集成电路(IC)技术进入深亚微米时代,片上系统SoC(System-on-a-Chip)以其显著的优势成为当代IC设计的热点。基于软硬件协同设计及IP复用技术的片上系统具有功能强大、高集成度和低功耗等优点,可显著降低系统体积和成本,缩短产品上市的时间。IP核是SoC设计的一个重要组成部分,已成为目前微电子设计的热点和主要方向[1]。

UART 核以其可靠性、传送距离远的特点被广泛应该到通信系统和 嵌入式 微处理器上。利用传统的EDA工具通过对RTL代码仿真、验证、综合、布局布线后生成网表, 下载 到FPGA中实现,这样做成的核主要用于验证的[2],不适合用来做掩膜。在ASIC/SoC技术日渐成熟的今天,设计商更希望得到能够做掩膜的IP核,从而便于嵌入到ASIC/SoC设计中。本文描述的UART核采用SYNOPSYS软件的设计流程,在RTL级上进行优化,解决了综合优化中碰到的一些常见问题。利用VCS 仿真、编写 测试 激励来验证,最后用design compile 综合优化做成的IP核可以满足此要求,应用到ASIC/SoC设计中将产生巨大的效益。

2、UART核的功能分析和设计

2.1 UART 核的传输 协议 与总体模块设计

通常信息是通过数据帧来传送的,由起始位、8位数据位、停止位组成。起始位为低电平,表示串行数据开始传输,停止位为高电平,表示数据传送结束。

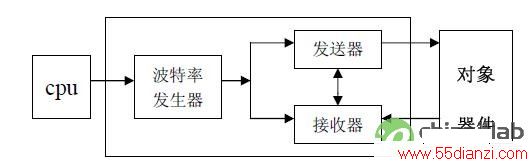

UART的结构框图如图1所示[3],主要有由波特率发生器、发送部分和接收部分等组成。本设计采用全双工异步通信的方式,通过层次结构化、划分模块的方法来实现。

图1 UART 的结构框图

2.2 UART 核的功能设计

2.2.1 波特率发生器

波特率是用来实现数据接收和发送的异步,波特率实际上就是分频器。UART的数据接收和发送是通过对波特率的设置进行实现的,本文采用16分频[3]。

2.2.2 接收器模块设计

接收器模块将8 位串行数据并行发出,用loadbuf 信号来装载八位串行数据。接收8位串行数据之前先要判断起始位;当起始位到来后经过5个clk16x采样,使采样点接近中央位置,这样数据稳定。然后每过16个时钟clk16x后,将8位串行数据逐位接收进来。当数据接收完毕,检查是否到达停止位,若是则表示接收成功,否则出现帧错误(framing_err), 并重新检测等待。当数据接收完毕后,等待数据的并行发出,当中断信号(rask)有效时发送数据。

接收数据停止位的判断采用9位移位寄存器(shift_reg)来实现。开始时将shift_reg全部置1,当16个clk16x到来时候,将串行数据从低位到高位逐位地移入到shift_reg的低位到高位。每接收一位数据后,判断是否接收完,由于起始位是最先进入shift_reg的,所以当数据全部接收完后。起始位已经进入了shift_reg的最后一位,表示数据接收完,如果在接收到停止位的逻辑是0,则表示产生帧错误(framing_err),等待再次检测直到停止位为1,表示接收完毕。采用状态机来实现数据起始位、停止位的判断和串行数据的接收[4]。

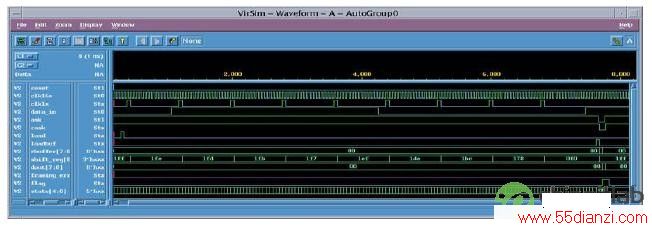

图2给出了接收模块的仿真波形。由波形可以看出,当输入0F0H,并行输出正确,其中state、reset、clk1x、flag、dout和rbuffer分别是状态机、复位信号、使异步的时钟同步、数据发送出去的标志、并行数据输出和数据缓冲器,而ask、rask和flag是中断发送控制,其中rask是控制数据发送。

图2 接收模块的仿真波形

2.2.3 发送器模块设计

发送器模块将8位并行数据串行发出,用wr写信号装载并行进来的8位数据到9位移位寄存器(shift_reg)的低8位,最高位置为0,表示数据的起始位,数据发送完后发送1。

数据发送前先发送1表示等待数据的到来。等待16个clk16x之后,先发送一个1,再过16个clk16x之后,发送起始位0;以后每过16个clk16x,发送一位数据,直到数据发送完。16个clk16x用计数器设计,数据发送用状态机实现。为了避免时序问题以及保证可 测试 性,采用单时钟沿同步触发,在15个clk16x到来时,将clk1x置1,在下一个clk16x时钟的上升沿到来后发送一位数据,由于clk1x为高电平持续时间为一个clk16时钟周期,

也就是在clk1x的下降沿把一位数据发送出去。即

always@(posedge clk16x)

…………

if(clk1x==1)

…………

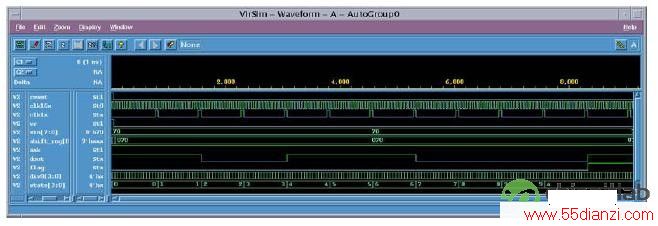

图3给出发送模块的仿真波形。由波形可以看出,当输入的并行数据是70H,串行输出正确,其中state、reset、clk1 x、flag和dout分别是状态机、 复位信号、使异步的时钟同步、数据发送出去的标志和串行数据输出,而div8和ask分别是4位计数器和中断请求信号。

图3 发送模块的仿真波形

3 UART 核的仿真、验证与综合、优化

3.1 UART 核的仿真和验证

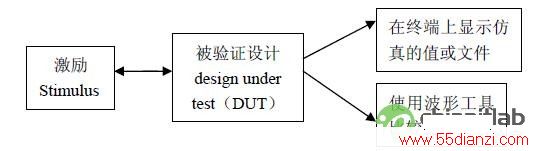

UART的功能仿真与验证通过测试平台(testbench)使用SYNOPSYS软件的VCS工具,其流程如图4所示[5]。接收和发送数据的正确性已通过图2和3所示仿真波形验证了。

图4 基于testbench 的仿真流程

3.2 UART 核的综合、优化

3.2.1 综合存在的问题

一般在UART设计中,采用多时钟,电平触发,并且判断数据的起始和停止采用额外的 存储 器或计数器,这必然给验证和综合优化带来时序上的问题,同时会产生毛刺和亚稳态,使得电路设计不够完善。

3.2.2 毛刺的解决

在通常的UART设计中存在组合逻辑,当输入的信号由高电平变低电平而其它某个信号由低电平变高电平时,由于在信号变化的瞬间,组合逻辑的输出并非同时变化,而是有先后之分,将导致输出出现尖脉冲,即产生毛刺。本文采用时钟沿(上升沿)触发,即将组合逻辑输出端通过加到寄存器后输出,从而避免毛刺的产生。

3.2.2 多时钟与亚稳态的解决

在通常的UART设计中,由于CPU时钟与UART的数据接收、发送时钟是处在不同的时钟域,时钟频率和相位上存在差异,导致时序不能满足建立时间和保持时间的要求,即数据的输出处于不确定状态,从而出现时序违反(slack<0)和亚稳态。本文通过采用同步电路设计,有效地解决时序和亚稳态的问题[6][7]。

3.2.3 UART 核的综合与优化

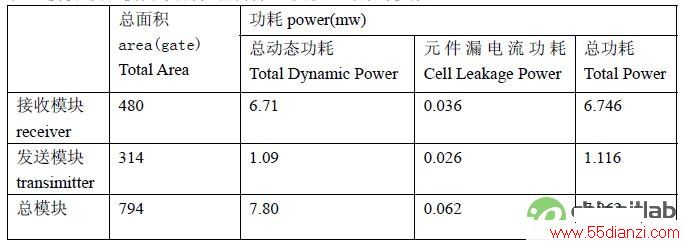

通过对RTL级进行优化,再仿真验证正确后,可以对UART核进行综合优化。本文采用SYNOPSYS软件的design compile进行综合优化,利用tcl(tool command language)语言编写综合优化的脚本。采用0.35um的工艺,将时钟周期设置为5ns,在满足时序(slack>0)的基础上经过综合优化,生成的时序、功耗、面积等参数如表1所示,优化后的功耗和面积满足了ASIC/SoC的要求。表1 接收/发送模块综合得出的功耗、面积、时序等参数

4 结束语

本文利用SYNOPSYS软件设计IP核,更适合用于ASIC/SoC设计,而采用传统的EDA软件实现的则适合用在FPGA上,不适合用来做掩膜生成ASIC/SoC。本UART核的逻辑设计采用VerilogHDL语言,用状态机和移位寄存器设计使整个设计的时序清晰,同时减少了接收模块停止位的判断,通过对RTL级优化避免了毛刺、亚稳态、多时钟等问题,仿真和验证采用的是SYNOPSYS软件的VCS,通过对时序、功耗、

面积的综合考虑,最后通过SYNOPSYS软件的design compile 综合优化完成的IP 核可成功应用到ASIC/SoC 设计上。

本文作者创新点是利用SYNOPSYS软件设计IP核,适合直接应用到ASIC/SoC设计中,并对RTL级做了优化,消除了在UART设计中碰到毛刺、亚稳态、多时钟等问题;通过测试平台(testbench)来仿真和验证,RTL 代码精简,时序、面积和功耗都做了优化,达到了IP核的要求。