3) 各存储器内部与之间的DMA传输的性能测试

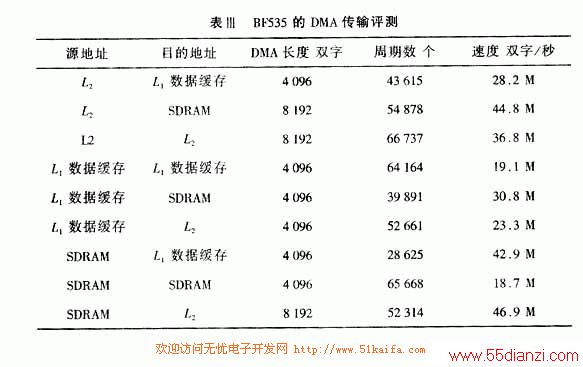

BF535支持不同存储器之间的块数据DMA传 输,带宽为32 bit,支持32 bit(双字)、16 bit(字)和8bit(byte)三种DMA传输方式。需要注意的是,当传输以16 bit和8 bit传输进行,只用到了部分的DMA带宽资源,剩下的资源将被浪费掉。表Ⅲ给出了32bit DMA传输模式下的速度指标,对于16 bit和8 bit传输时,传输速度保持不变,但是单位分别改为字/秒和字节/秒。在存储器DMA的同时,BF535可以同时进行其他操作,只要DSP核心不访问DMA正在读写的地址区域,就不会引起总线冲突。认识到这一点,对于提高BF535的效率而言至关重要。测试环境:DSP核心时钟fCCLK为300M Hz;系统时钟fSCLK为fCCLK的2.5倍分频,工作在120M;SDRAM为PC133标准。测试样本数目为15。

从表Ⅲ中的实测数据可以看出,DMA的速度均在18.7 M双字/秒以上,最高速度达46.9M双字/秒,满足绝大多数高速数据采集系统的速度要求。从表Ⅲ的数据同时可以得出以下结论:

(a) DMA双向速度不对称,将源地址和目的地址交换以后,传输速度会发生变化。低速存储器区域向高速区域传输时,要比反向传输快。

(b) 存储器区域内部DMA速度一般比区域之间DMA要慢,如L1→L1比L1→L2和L1→SDRAM都要慢一些。其它区域也有类似现象。

(c) 对于同种存储器内传输,高速存储器区域内部DMA速度并不一定快,如L1→L1 DMA比L2→L2慢一些。对于同种存储器内,DMA传输速度并不比通过核心寄存器访问存储器占优势,如后者在L1数据缓存内完成一次32位数据的搬移,速度可以到75M双字/秒。

3 结束语

本文对BF535的存储器机制进行了分析和评估,测试数据证明,BF535具有优良的存储器性能。文章基于BF535测试,对AD公司的Blackfin系列的其它产品也有重要的参考作用;对于已经推出的BF532和即将推出的BF531、BF533而言,这三者的核心设计和BF535没有任何区别。主要的变化有:根据不同的用户群,对BF535的外部接口进行了简化,对L1和L2进行了增加或者减少,在DSP的核心运行速度上也进行了调整。开发者在使用后续产品时,根据上面所提供的测试数据,适当换算一下即可估算出其它产品的存储器性能。实践证明,这种估算方法是真实可信,行之有效的。

[1] ADInc.,ADSP-21535 Blackfin DSP Hardware Reference [R],November 2002.

[2] ADInc.,Blackfin DSPINstruction Set Reference[R],Octo-ber 2002.

[3] ADInc.,ADSP-21535 EZ-KITLITE.Evaluation SystemManual[R],May 2002.

[4] ADInc.,EE-171:ADSP-21535 Multi-cycle Instruc-tions and Latencies[R],September 10,2002.

[5] ADInc.,ADSP-21535 Preliminary Data Sheet(Rev.7-02)[R],June 2002.

[6] ADInc.,NR002556B:Blackfin ADSP-21535 Anomalylist[R],December 2002.