��������

�������Ǽ��������װ�õĻ�����Ԫ�������а���ǰ�����롮���䡯�����Ĺ��ܣ�һ���������ܴ���һλ�����ƴ��롣�������Ǽ������ܼ�����г��õļ��д�������

1��R-S������

R-S������������������ͼ��ʾ��������������ˣ���������ˡ����У�SΪ��λ�ź�����ˣ�RΪ��λ�ź�����ˣ�Q��Q��Ϊ����ˡ��涨QΪ�ߡ�Q��Ϊ��ʱ���ô�����Ϊ1״̬����֮Ϊ0״̬������ֵ�����¡�

����

���

S��

R��

Q

Q��

0

0

��ȷ��

��ȷ��

0

1

1

0

1

0

01

1

1

1

���ֲ���

���ֲ���

2��D������

D�������ֳ����ݴ���������������������ͼ��ʾ��R��S�ֱ�Ϊǿ����0����1�ˣ���������״̬����ʱ������CLK�����ص���ʱD�˵�״̬���֡���D=1ʱ��������Ϊ1״̬����֮Ϊ0״̬������ֵ������

ʱ������

����

���

D

Q

![]()

0

0

![]()

1

1

3��J-K������

J-K�����������������£�R��S�ֱ�Ϊǿ����0����1�ˡ�KΪͬ����0����ˣ�J�ͬ���?����ˡ���������״̬����ʱ������CLK�½��ص���ʱJ��K�˵�״̬����������ֵ������

ʱ������

����

���

J

K

Q

![]()

0

0

����

![]()

0

1

0

![]()

1

0

1

![]()

1

1

��ת

J-K�������������ܱȽ�ȫ�棬����ڸ��ּĴ������������������Ƶȷ���Ӧ����Ϊ�㷺������ijЩ�����������Ƽ�������λԪ���ۼӵȣ�����D������������D��������·���£����Դ���Ӧ������λ�Ĵ����ȷ��档

�Ĵ�����

�Ĵ������ɴ�������ɵģ�һ����������һ��һλ�Ĵ���������������Ϳ������һ����λ�ļĴ��������ڼĴ����ڼ�����е����ò�ͬ���Ӷ���������ͬ�����õ��л���Ĵ�������λ�Ĵ������������ȡ��������Ǿͼ�����������Щ�Ĵ����ĵ�·�ṹ������ԭ����

1������Ĵ���

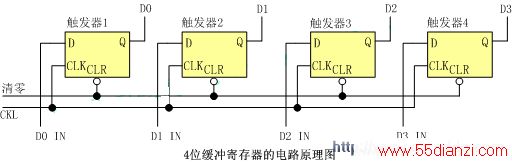

���������ݴ�ij�����ݣ��Ա����ʵ���ʱ����ĺ����ļ��㲽�轫���������������������䵥Ԫ��ȥ����ͼ��һ���������롢���������4λ�������ĵ�·ԭ��ͼ������4��D��������ɡ�

����ʱ����������˼��������壬�Ѹ���������0����Q��Ϊ0��Ȼ�����ݼӵ���������D����ˣ���CLKʱ���ź������£�����˵���Ϣ�ͱ����ڸ��������У�D0~D3����

2����λ�Ĵ���

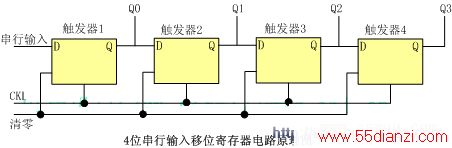

��λ�Ĵ����ܽ��������������λ����������ƶ����Դﵽ��������й���������Ĺ��ܣ��뿴��ͼ

����ʱ����������˼��������壬ʹ�����������0��Ȼ��һ������D0�ӵ�������1�Ĵ�������ˣ��ڵ�һ��CLK�����������Q0=Q0��Q1=Q2��Q3=Q0����ڶ�������D1�ӵ���������ˣ��ڵڶ���CLK���嵽��ʱ��Q0=Q1��Q1=Q0��Q2=Q3=0���Դ����ƣ������ĸ�CLK����֮������˷ֱ���Q0=Q3��Q1=Q2��Q2=Q1��Q3=Q0��������ݿ��ô��е���ʽȡ����Ҳ���ò��п�ʽȡ����

3��������

������Ҳ�������ɸ���������ɵļĴ����������ص����ܹ��Ѵ�������е����ݼ�1���1��������������Ҳ�ܶ࣬���в���������ͬ���������ȣ��������Ǿ����в������������������ܡ�

��ͼ����һ����J-K��������ɵ��в��������Ĺ���ԭ��ͼ�����ּ��������ص��ǣ���һ��ʱ�������ʹ�������Чλ��1��ʹ����0��1���ڶ���ʱ�������ʹ�����Чλ��1��0��ͬʱ�ƶ��ڶ�λ��ʹ����0��1��ͬ�����ڶ�λ��1��0ʱ��ȥ�ƶ�����λ��ʹ����0��1����������ˮ��ǰ��һ����λ��λ��ȥ��

��ͼ�и�λ��J��K����˶��������ģ����൱��J��K����˶�����1�״̬������λ����������ת��״̬��ֻҪʱ���������һ�������ұߵĴ������ͻᷭת����Q��0תΪ1����1תΪ0��

��ͼ�е������������4λ�ģ���˿��Լ�0~15���������Ҫ�Ƹ����������Ҫ����λ������8λ�������ɼ�0~255������16λ��ɼ�0~65535������

���Ĺؼ��֣�������ϵ��ʽ51��Ƭ������Ƭ��-�����豸 - 51��Ƭ��