2�����첽ͨ�ŵ�֡��ʽ�Ͳ�����

2.1 �����첽ͨ�ŵ�֡��ʽ

�ڴ����첽ͨ���У�����λ�����ַ�Ϊ���͵�λ������λ��ǰ����Ҫ����ʼλ��ֹͣλ�����������ֹͣλ��ǰ�����һ������λ(bit)��У��λ����֡��ʽ��ͼ1��ʾ��

��ʼλ��һ����0�����Ǽ���ÿһ֡�Ŀ�ʼ��Ϊ�����������ݽ����豸�������ݣ��ڽ�������λ�������ֱ������ȥ������λ���ݴ���ͨ��Э�飬����������ַ����ȿ���Ϊ5��6��7��8λ��ͨ������λΪ7λ��8λ�����Ҫ�����ASCII���ݣ�����ʹ����չ�ַ����õ��ı����߶��������ݣ�������λ��ʽ����Ҫ����8λ������λ������ʱ��һ���ַ������λ���ݿ�ʼ�����λ���������������ĸC��ASCII������ʮ����67�������Ƶ�01000011����ô����Ľ���11000010��У��λ��Ϊ����֤����������Ƿ���ȷ���գ�������У�鷽�����桢żУ�顣����У��λҲ����Ϊ0У�����1У�飬����������λ��1�ĸ����Ƕ��٣�У��λʼ��Ϊ0����1������ڴ���Ĺ�����У��λ�����˱仯�������ʾ������ij����������ڴ������ݵ�ʱ��Ҳ���Բ���У��λ��ֹͣλ��Ϊ��1������ÿһ֡��ĩβ��������1λ��1.5λ����2λ����õ���1λ������1λ��ֹͣλͨ�������������ij��ϣ��ڴ�����һ���������������ַ�֮ǰ�����豸Ҫ��ʱ�䡣

2.2 �����첽ͨ�ŵIJ�����

���п�ÿ�뷢�ͻ�������ݵ�λ��Ϊ�����ʡ������ͻ����һλ������Ҫʱ��Ϊt��������Ϊ1/ t,��Ӧ�ķ��ͻ����ʱ��Ϊ1/t Hz�����ͺͽ����豸�IJ�����Ӧ�����ó�һ�£�������ߵIJ����ʲ�һ�£��������У�������֡����

3 ���з��͵�·�����

Ϊ��·��Ƶĸ����ԣ����õ�֡��ʽΪ�� 1λ��ʼλ+8λ����λ+1λֹͣλ��û��У��λ��������Ϊ9600��

3.1 �����ʷ����������

Ҫ����9600�����ʣ�Ҫ��һ��������9600 Hz��ʱ�Ӳſ��ԡ�Ϊ�����߾��ȵ�ʱ�ӣ���ѡ��6MHz��6M������9600���ľ������ṩ�ⲿʱ�ӡ���Ȼ����Ҳ����ѡ����Ƶ�ʵ�ʱ��������9600 Hz��ʱ�ӡ�����6MHzʱ�ӣ���Ҫ���һ��625���Ƶķ�Ƶ��������9600�����ʵ�ʱ���źš���VHDL��Ʒ�Ƶ���ϼ�������Ͳ��ٸ���Դ�����ˡ�

3.2 ���͵�·�����

���ݲ��õ�֡��ʽ,��Ҫ���͵�����Ϊ10λ(1λ��ʼλ��8λ����λ��1λֹͣλ)���ڷ�������10λ��Ӧ��ֹͣ���ͣ���ʹ���Ͷ˵�ƽ������1��Ȼ��Ⱥ��´εķ��͡�������ʵ���������ܵ�VHDLԴ����

library ieee;

use ieee.std_logic_1164.all;

entity Com is

port(clk,en:in std_logic;

Send_data:in std_logic_vector(9 downto 0);

serial:out std_logic);

end com;

architecture com_arc of com is

begin

process(clk)

variable count:integer range 0 to 9 :=0;

begin

if en=��0�� then

count:=0;

serial<=��1��;

elsif rising_edge(clk) then

if count=9 then

serial<=Send_data(9);

else

serial<=Send_data(count);

count:=count+1;

end if;

end if;

end process;

end com_arc;

���У�Send_data(0 to 9)��ʾ��Ҫ���͵�����֡������ʱ����ʼλSend_data(0)����Ϊ��0��ֹͣλSend_data(9)����Ϊ��1��������Ӳ����·���ӵ��豸���յ������ݻ���ִ����ڷ���ÿһ֮֡ǰ�����ȸ������enһ���͵�ƽ���壬�õ�·��λ(count��0)��Ȼ��ʼ���͡�����count �ڽ�����������¼���͵�������Ŀ��������֡��������Ͷ˾�һֱ����ֹͣλ(��1)��

3.3 ʱ�����

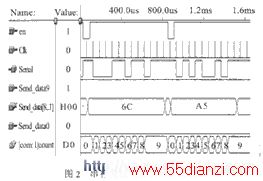

ѡEDA���ߣ���VHDLԴ������롣�õ��� ALTEra��˾��MAX+plus II 9.3 Baseline���������֧��VHDL�ı��롢���档ͼ2�DZ����ķ����������У�ClkΪƵ��9600Hz��ʱ�ӣ�Send_data0Ϊ��ʼλ��Send_data[8..0]Ϊ����λ�� Send_data9Ϊֹͣλ�������ʾ�������ȫ�ǰ�����֡��ʽ���͵ġ�

4 ���н��յ�·�����

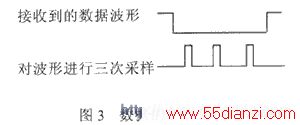

���յ�·�ȷ��͵�·Ҫ���ӣ����յ�·Ҫʱʵ�����ʼλ�ĵ�����һ������ʼλ������Ҫ����һ֡���ݽ���������Ϊ��߽��յ�ȷ�ԣ����������ʣ�ÿһλ���ݶ���3��Ƶ�IJ����ʶ����ݽ��в�������ͼ3��ʾ����Ȼ���3�β�����������о������3�β�����������2��Ϊ�ߵ�ƽ���������һλ���ݱ��о�Ϊ�ߵ�ƽ�����ߣ�Ϊ�͵�ƽ��

4.1 �����ʷ������Ͳ���ʱ�ӵ����

Ϊ���3�β���������Ƶ��Ϊ9600Hz�Ľ���ʱ���⣬��Ҫ��һ��3��Ƶ�IJ���ʱ�ӡ�������ʵ���������ܵ�VHDLԴ����

library ieee;

use ieee.std_logic_1164.all;

entity count625 is

port(clk,en:in std_logic; CLOCk1,Clock3:out std_logic);

end count625;

architecture count625_arc of count625 is

begin

process(clk,en)

variable count:integer range 0 to 625 :=0;

begin

if en=��0�� then

NUll;

elsif (rising_edge(clk)) then

count:=count+1;

if count=625 then

Clock1<=��1��; count:=0;

else

Clock1<=��0��;

end if;

if (count=100 or count=300 or count=500 ) then

Clock3<=��1��;

else

Clock3<=��0��;

end if;

end if;

end process;

end count625_arc;

����clkΪ6MHz��ʱ�ӣ�en���Ʋ��εIJ����� Clock1Ϊ9600Hz�Ľ���ʱ�ӣ� Clock3Ϊ3��Ƶ�IJ���ʱ�ӡ�

4.2 ���յ�·�����

���н��յ�·����Ҫ���жϽ������ݵĵ�������ÿһ֡�Ŀ�ʼ��Ȼ������ݽ���3�β���������о������Ϊ����ƣ�֡��ʽ��Ȼ����1λ��ʼλ+8λ����λ+1λֹͣλ����������ƵĽ��յ�·VHDL����

library ieee;

use ieee.std_logic_1164.all;

entity com_receive10 is

port(com,clr,clk1,clk3:in std_logic;Q:out std_logic_vector(0 to 9);Valid:out std_logic);

end com_receive10;

architecture com_receive10_arc of com_receive10 is

Signal Enable:std_logic :=��1��;

Signal Hold:std_logic :=��0��;

Signal N:std_logic_vector(0 to 2) :="000";

begin

���Ĺؼ��֣�ͨ�� 51��Ƭ������Ƭ��-�����豸 - 51��Ƭ��

��һƪ��89S51�Ŀ��Ź��÷�