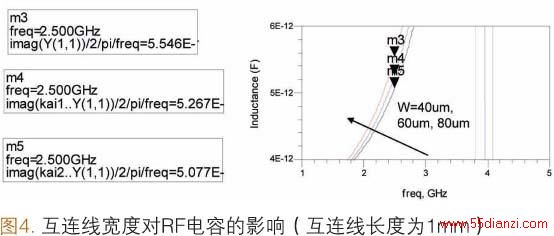

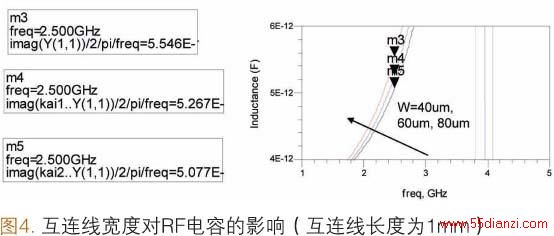

除互连线长度之外,互连线的宽度也会对RF电容产生影响。在衬底的制作过程中,线宽通常会发生变化(举例来说,与设计宽度相比,实际线宽的变化范围为±10.0μm~±15.0μm)。如图4所示,如果设计的互连线为1.0mm长,60.0μm宽,实际却达到40.0μm宽,在2.5GHz下等效电容变化将达到5.3%(以3.0pF接地SMD电容为例)。如果把这种SMD电容用于滤波器中,对于RF应用来说,电容值5.3%的变化将导致约2.7%的频移。我们必须对RF应用中含有SMD电容的RFSiP模块的衬底制造容差进行细致研究。

具有互连线容差的阻抗特性和引线键合电感

具有互连线容差的阻抗特性和引线键合电感在RFSiP中,RF沟道中通常要使用差分方式。大多数收发机和LNA采用差分输入/输出信号模式,从而获得更好的噪声抑制特性。由于需要额外的空间,以保证特定互连线的宽度和间隔,并保持互连线与接地屏蔽/平面之间的距离,因此在封装产品中这些平行互连线的排列技术极具挑战性。线宽/间隔容差对差分对的阻抗特性具有极大的影响。如果不能很好地控制这一容差,结果仍将显示出差分信号特性,但回程损耗和插入损耗将极大地增大,从而不再具有良好的匹配特性。

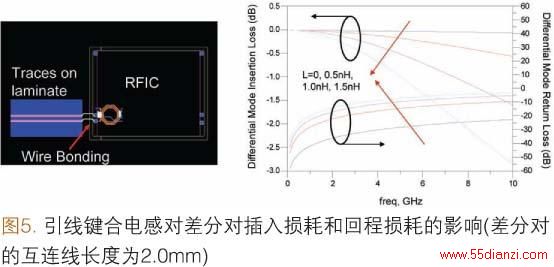

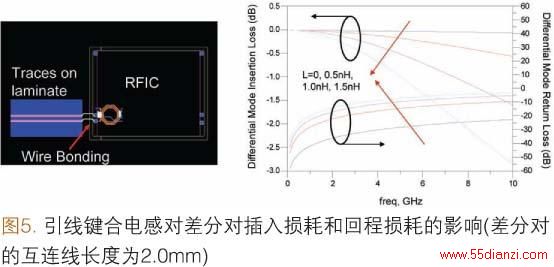

图5显示了键合引线电感是如何影响差分对连线的插入损耗的。在实例中,100.0Ω差分对的长度为2.0mm。假设差分对的一端使用引线键合方式与RFIC连接,并把直接与引线长度相关的电感(L)设为可变值。正像回程损耗曲线图表示的那样,加上引线键合电感可使差分对偏离100.0Ω这一匹配条件,结果使插入损耗增大。在5.0GHz下,0.5nH、1.0nH和1.5nH引线电感的插入损耗分别为0.2dB、0.5dB和1.2dB。即使达到极高的频率,叠层上的差分对本身仍具有良好的阻抗匹配特性。

这一点也在图5(L=0nH的情况下)中表示出来,回程损耗在频率高达10.0GHz时保持良好,这表明100.0Ω差分对本身具有良好的匹配和低损耗特性。显然,在高频RFIC应用中,引线键合损耗成为显著的问题。为了克服这一阻抗失配问题,RFIC和封装设计师应协同工作,寻找与特定芯片阻抗相匹配的封装形式。这样可能出现非标准差分对设计,但是该设计将与引线键合芯片非常匹配。

对于高频RF封装来说,倒装芯片解决方案可实现最小的互连电感,从而获得期望的优良性能(低损耗、良好匹配)。但是用于引线键合结构中的RFIC设计不能直接用于倒装芯片产品,即使使用了RDL(重新分布层)也是如此,主要是因为RFIC中的电感在倒装芯片结构中所处的环境条件与引线键合结构中截然不同。

BBIC和RFIC主时钟线之间的串扰把BBIC和RFIC封装在单个封装系统(SiP)中时,BBIC和RFIC信号可能出现相互干扰。根据傅立叶分析法,BBIC(假如在20.0MHz或40.0MHz时钟速度下)中的主时钟信号线将产生高频信号作用。以40.0MHz时钟速率为例,其傅立叶级数到第60位时的频率为60×40=2400MHz,符合WiFiRFIC(2.4GHz-2.5GHz)通带的范围。由于主时钟线路通常与BBIC中几个电路元件相连接以获得功能性,因此靠近RF电路的可能性很大。在这种情况下,RF电路可能成为主时钟信号的受害者,而产生于时钟线的耦合信号将变成噪声,不仅可能增大RF电路的噪声系数,还可能降低RF电路的选择性。

为了对主时钟线和RF元件之间的相互作用进行分析,把压控振荡器(VCO)中使用的RF电感(6.0nH)放置在穿通多层衬底的时钟互连线附近(图6)。我们在这个研究中使用的互连线长为2.0mm。当VCO电感和互连线之间的横向距离(d)大于0.5mm时,产生的耦合信号将小于-80.0dB。耦合信号的实际要求由SiP系统级电设计决定。

本文关键字:暂无联系方式电工文摘,电工技术 - 电工文摘