3D叠层芯片解决方案中主时钟线与RFIC之间的串扰

使用叠层芯片法可以缩小封装的整体面积,这种方法已广泛应用于几种复合器件封装中:存储器与控制器、存储器与DSP以及其它数字应用。这种方法可以用于RFSiP封装中吗?在回答这个问题之前,我们应先了解RFIC的特殊性。

RF电路对任何邻近的东西都非常敏感。正如我们了解的那样,附近的接地面或互连线都会影响RF电感值,从而影响RFIC的特性。在某种程度上,RF电路通常成为其它邻近元件的受害者。

举例来说,在叠层芯片结构中如果只使用BBIC和RFIC,它们之间的垂直距离只是BBIC或RFIC的厚度。正如我们了解的那样,在大多数应用中扁平封装外形通常都是优良的品质因数。因此,芯片的厚度受到限制。在这种扁平外形封装中,使BBIC和RFIC之间保持良好的隔离并不是件容易的事。

为了在BBIC和RFIC器件之间实现最佳隔离特性,可以在它们之间使用一个金属屏蔽层。但是这种方法将带来意想不到的问题。首先,金属屏蔽可能影响RFIC的性能,对我们所期待的响应产生潜在的“失调”作用。RFIC设计过程中应对金属屏蔽效应产生足够的重视,使之在后续的SiP叠层芯片结构设计中不再出现问题。因此IC设计师和封装设计师在IC设计之前就应多方沟通。第二,增加金属屏蔽层可能增加组装成本,从而增加产品的最终成本。在今天这种成本导向市场的时代,只有降低成本才能获得高优先权。

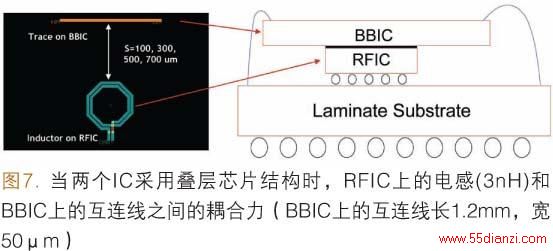

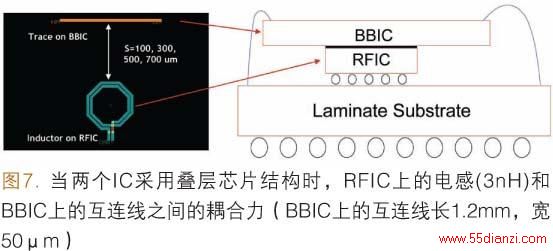

图7给出了BBIC和RFIC采用SiP(为简单起见,实例中未表示SMD元件)叠层芯片结构的实例。在这个实例中未使用金属屏蔽层,使用环氧芯片粘接材料把BBIC直接堆叠在RFIC上。就像前文提到的那样,BBIC中的主时钟信号(20.0MHz或40.0MHz)包含一些高频成分,落在RF芯片通带的范围内。如果BBIC中时钟互连线和RF芯片之间没有保持足够的隔离,特别是在VCO电感中,主时钟信号可能使RF电路产生噪声,降低RF芯片的选择性。

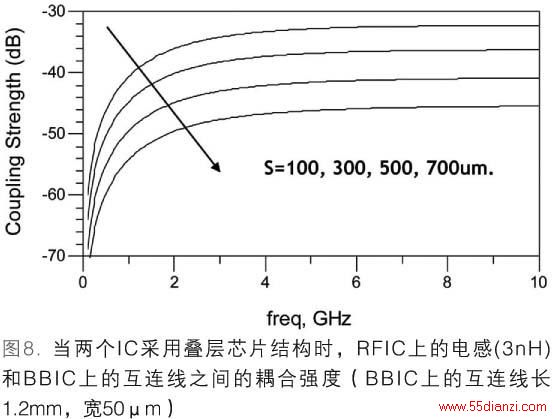

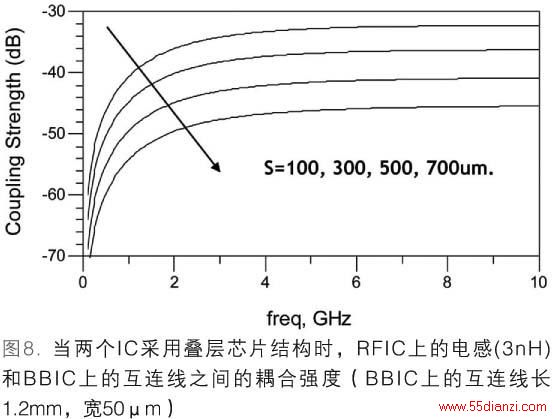

图8表示了BBIC和RFIC电感之间的耦合强度(未使用隔离层)。假设BBIC和RFIC的厚度为250.0μm时,对VCO电路中的3nH电感进行了研究。BBIC中主时钟的互连线设置为1.2mm长。根据模拟结果,当横向距离(S)为100.0μm时,2.5GHz下的隔离为-35dB。这一隔离值对大多数RF应用来说是不够的。当横向距离为700.0μm时,隔离值提高为-50dB,这个值对大多数RF应用来说仍然不够。为保证VCO电感的性能,位于BBIC电感上方的主时钟不能使用长互连线。根据以上分析,我们还应对RFSiP使用的叠层芯片法做进一步研究,从而判断BBIC和RFIC器件之间出现严重相互干扰的可能性。

RFSiP技术为更小外形因数RF产品的发展铺平了道路。除了板级封装和SiP方法存在的共性问题(互连线长度和宽度、SMD焊盘寄生效应、阻抗匹配等)以外,SiP产品还存在一些特殊问题或担忧,在成功实现这种产品之前必须解决这些问题。在板级封装中,一旦每块电路/元件的功能正常,整个系统就可以正常工作,因为单个部件在系统中与它们单独工作时的状况基本相同。

对于SiP来说,当所有的部件被挤进狭小的区域,并且在叠层中采用致密布线时,肯定会出现更多的串扰,从而使RF电路响应出现“失调”。因为涉及到多种不同的技术,需要建立通用模拟平台,从而进行系统级鉴定。芯片电路设计(引脚排列等)和SiP设计技术应并行发展,特别是在早期设计阶段,这样才能在芯片和SiP要求之间进行权衡,避免在后序形成系统时出现电冲突问题。

本文关键字:暂无联系方式电工文摘,电工技术 - 电工文摘