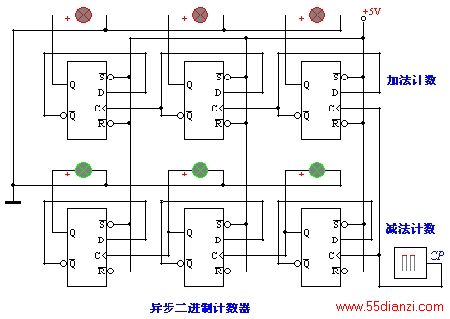

异步二进制计数器在做“加 1 或减 1 ”计数时,是采取从低位到高位逐位进位或借位的方式工作的。因此,各个触发器不是同时翻转的。

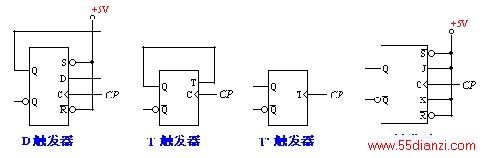

组成二进制计数器的各个触发器均连接成计数方式,如下图所示。

所谓触发器计数方式,就是使触发器进行“求反”操作,即 ![]() 。多级计数器的每一级触发器,实际上也只作“求反"操作,只是在前级进(借)位时才执行这种操作。在设计二进制加法计数器时,当前级

Q 端为高电平时,预示将要进位,当 Q 端由高电平转为低电平的时刻,后级应完成一次加

1 ( 进位) 操作。由此想到,只要以前级的

。多级计数器的每一级触发器,实际上也只作“求反"操作,只是在前级进(借)位时才执行这种操作。在设计二进制加法计数器时,当前级

Q 端为高电平时,预示将要进位,当 Q 端由高电平转为低电平的时刻,后级应完成一次加

1 ( 进位) 操作。由此想到,只要以前级的 ![]() 作为后级 CP,就可以组成多级二进制加法计数器。同理,只要以前级的 Q 作为后级的

CP,就可以组成二进制减法计数器。电路结构如图示。

作为后级 CP,就可以组成多级二进制加法计数器。同理,只要以前级的 Q 作为后级的

CP,就可以组成二进制减法计数器。电路结构如图示。

① 电路结构

② 电路特点

这类电路的特点是 CP 信号只作用于第一级,由前级为后级提供驱动状态变化的信号。如图所示,第一级输出信号 Q 或 ![]() 的上升沿或下降沿滞后于CP 的上升沿( 传输延迟时间 )。以这种信号作为后级的驱动信号,使第二级的输出信号相对于CP 的延迟时间为两级电路的延迟时间。由于触发器的输出信号相对于初始的 CP 的延迟时间随级数增加而累加,故各级的输出信号不是同步信号,因而叫做异步计数器。

的上升沿或下降沿滞后于CP 的上升沿( 传输延迟时间 )。以这种信号作为后级的驱动信号,使第二级的输出信号相对于CP 的延迟时间为两级电路的延迟时间。由于触发器的输出信号相对于初始的 CP 的延迟时间随级数增加而累加,故各级的输出信号不是同步信号,因而叫做异步计数器。

上一篇:可予置计数器