同步二进制减法计数器是在计数脉冲驱动下,对计数器进行件1计数。

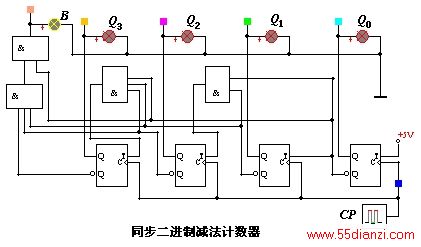

① 电路结构

根据二进制减发运算规则,每一次操作都是在 4 位二进制数的最低位减 1。

同步二进制减法计数器也由 T 触发器组成。最低位对每一个CP 都作变反操作,作一次减 1 运算。仅在各低位数皆为零时,若再减 1,就向高位借

1。由各低位级的

![]() 端,通过与门组合成给高位的借位信号。

端,通过与门组合成给高位的借位信号。

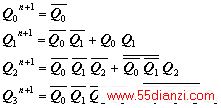

② 触发器驱动方程

由此推出,n 个 T 触发器组成的同步二进制减法计数器,触发器驱动方程通式为:

![]()

③ 电路状态方程和输出方程

根据T触发器的特性方程

![]() ,写出电路状态方程:

,写出电路状态方程:

输出方程:

![]()

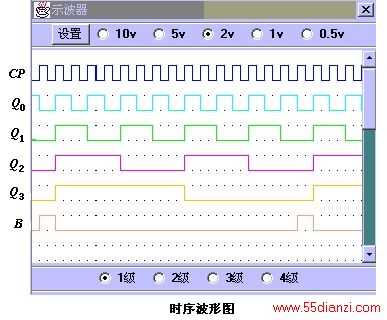

④ 时序波形图

动态模拟同步二进制减法计数器,由虚拟示波器观察时序波形图如下。计数脉冲 CP 上升沿驱动触发器状态改变。触发器初始状态,

![]() ,发出借位信号,当计数脉冲到来时,

,发出借位信号,当计数脉冲到来时,

![]() ,实现向高位借位。

,实现向高位借位。

⑤ 减法计数器用作定时器

用计数脉冲的节拍数进行时间控制,定时器在运行前由用户规定额定的节拍数,运行时累计拍数达到额定值时就停止计数,并输出指示信号。在用减法计数器作定时器时,可选与额定节拍数对应的状态为初态,例如额定的节拍数为 7,设定减法计数器初态为

![]() ,在计数器运行时,来一个计数脉冲,进行减

1 计数。当第七个计数脉冲到来后,计数器状态为

,在计数器运行时,来一个计数脉冲,进行减

1 计数。当第七个计数脉冲到来后,计数器状态为

![]() ,给出指示信号,并用此信号令计数器停止运行。

,给出指示信号,并用此信号令计数器停止运行。

上一篇:同步二进制加法计数器