和同步计数器不同,组成异步计数器的触发器不是共用同一个时钟源,由于各触发器不是使用同一个时钟源,所以触发器的翻转是异步的。常用的异步计数器有二进制异步计数器,十进制异步计数器等,异步计数器也有加法时序和减法计数。

23.4.1 二进制异步计数器

23.4.1.1二进制异步加法计数器

三位二进制异步加法计数器的电路图如图10-4-1。它由三个D触发器构成,每个D触发器接成T'触发器。每一级触发器有两个状态,三级共有23=8个状态,所以可以记下八个脉冲,第八个脉冲来到后电路返回初始状态。如果设初始状为Q2=Q1=Q0=0,那么电路在记数脉冲作用下将按状态转换表表23-8的顺序变化。

图23-4-1 二进制异步加法计数器

23.4.1.2 二进制异步减法计数器

有时需要将计数器的数一个一个减去,此时计数器的态序与加法计数器正好相反,其状态转换见表23-9。如果仍然使用图23-4-1中的下降边沿动作的D触发器,根据触发器翻转产生进位时刻的需要,进位时钟应该由前一级触发器的![]() 端提供,如图23-4-3所示。每一级触发器仍然是T’触发器,因此它的波形图十分好画,如图23-4-4所示。

端提供,如图23-4-3所示。每一级触发器仍然是T’触发器,因此它的波形图十分好画,如图23-4-4所示。

在构成二进制异步减法计数器时,也可以不改变图23-4-1中的进位信号,而改变触发器的时钟动作沿,用上升边沿动作的D触发器去取代下降边沿动作的D触发器。用上升边沿动作的D触发器构成的减法计数器如图23-4-4所示。改变进位信号是取自Q端或![]() 端;或者改变触发器的动作沿,这两种方法只要改变其中一项就会改变异步计数器的时序。根据状态转换表23-9和图23-4-3可以做出三位二进制异步减法计数器的波形图,如图23-4-5所示。

端;或者改变触发器的动作沿,这两种方法只要改变其中一项就会改变异步计数器的时序。根据状态转换表23-9和图23-4-3可以做出三位二进制异步减法计数器的波形图,如图23-4-5所示。

图23-4-4 二进制异步减法计数器

图23-4-5 二进制异步减法计数器波形图[动画5-2]

23.4.2 集成异步计数器

二进制异步计数器,除了二进制的以外,还有十进制、十二进制等等。不过非二进制异步计数器的分析不象异步二进制计数器和同步计数器那样简单,因为各个触发器的时钟不是接在同一个时钟源。所以,触发器是否翻转不但要看触发器数据端的条件,还要看是否有时钟的动作沿。

产品的集成异步计数器主要有三个:

74LS90(74LS290),2-5分频异步加法计数器

74LS92, 2-6分频异步加法计数器

74LS93, 2-8分频异步加法计数器

这三个计数器在电路结构上基本相同,下面介绍集成2-5分频异步加法计数器74LS90。

23.4.2.1 2-5分频异步加法计数器74LS90简介

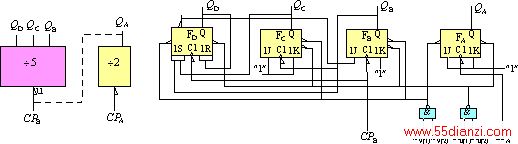

74LS90是应用很广的一款集成异步计数器,它是由2分频计数器和5分频计数器二部分构成的,除了供电电源是公用用的,2分频和5分频二部分是互相独立的。74LS90的简化方框图如图23-4-6(a)所示,其逻辑图如图23-4-6(b)所示。

(a)方框图 (b) 74LS90异步加法计数器逻辑图

图23-4-6 74LS90异步加法计数器逻辑图和方框图

由电路图可知时钟源CPA仅接向第一级触发器的时钟端,而QA是作为CPB和CPD使用的,QB又作为CPC使用。FA和FC、接成T′触发器,它们是否翻转就看有无CPA或CPC的动作沿,即下降沿的变化;FB和FD则还要看数据端的状态而决定其是否翻转。做十进制数时,QA到CPB的连线是在集成电路外部连接的。

1.计数器的时序

图23-4-6所示计数器由二个互相独立的部分组成,触发器FA是JK触发器,按T′触发器模式工作,实际上就是2分频计数,这里几分频的提法相当是进制。所以我们只需要分析5分频的部分,即5进制计数器的部分就可以了,二个部分级联起来,就构成十进制计数器。图中的触发器是下降沿翻转的触发器,前面讨论过二进制异步计数器由T′触发器串联而成,时钟端的连线因触发器的触发沿和计数器时序不同而异,可构成N=2n循环周期的计数器,在分析非二进制异步计数器时,确定触发器的触发方式同样重要。5分频部分触发器数据端的驱动方程式如下:

(a)方框图

本文关键字:计数器 电子技术,电工技术 - 电子技术

上一篇:同步计数器的分析