(3) 电源/地线上杂散电容/电阻效应

虽然深亚微米集成电路中的改良设计能够充份保护IC内部电路,避免异常的ESD损伤。但是在电源/地线上的寄生电阻与电容效应会降低改良电路的保护效果。因为ESD放电现象在很短的时间内(约l00ns)便会出现高达数安培的放电电流,如果该改进ESD箝制电路的位置距离ESD的输入或输出脚位太远,则可能会发生时间上来不及启动保护电路的现象。在深亚微米VLSI中,芯片的尺寸越来越大,相对地环绕整个芯片的VDD与VSS电源线更长,其所相对产生的杂散电容/电阻效应也会增加,这反而降低了ESD箝制电路的防护效果。

(1) 工艺上的改进

为了提高深亚微米集成电路的抗静电能力,目前有ESD注入、金属硅化物扩散层分隔和N阱电阻三种ESD保护改进工艺应用于深亚微米集成电路制造过程中。

为了克服因LDD结构所造成电路抗静电能力的下降.便出现了ESD注入工艺。其原理是在同一电路上做出两种不同的NMOS元件,一种是给内部电路单元使用,具有LDD结构的NMOS元件;另一种是给I/O使用,不具有LDD结构的NMOS元件。但利用ESD注入过程做的元件拥有较深的结面深度,故会有较严重的横向扩散作用,所以利用ESD注入过程所作的NMOS元件不能用太短的沟道长度。此外利用ESD注入工艺做的NMOS元件与LDD结构的NMOS元件不同,故需要额外的处理及设计来提取这种ESD注入工艺NMOS元件的SPICE参数,以利于电路模拟与设计工作的进行。另外一种ESD注人工艺是将一掺杂浓度较高的硼注人到接触孔正下方的N型扩区和P型衬底之间,以降低该结面的击穿电压。因为该结面具有较低的崩溃电压,当静电放电出现在NMOS元件的漏极时,静电放电电流便会先由该低击穿电压的结面放电。利用这种工艺过程,NMOS元件仍可使用LDD结构且具有较短沟道长度,且该NMOS元件的SPICE参数跟其他NMOS元件相同,除了该结面击穿电压之外,不必另外抽取这种ESD注入的NMOS的SPICE参数。

为了提高输出级的ESD能力,在工艺上还开发出了金属硅化物扩散层分隔工艺。其原理是把输出级用的NMOS元件中的金属硅化物去除,使其源极和漏极的方块电阻值回到30~40Ω/□,从而提高MOS元件的抗静电能力。

在深亚微米集成电路制造工艺上还采用N阱电阻的方法来提高电路的抗静电能力。原理是将输出NMOS管漏极的N+扩区断开,位于中间的N+扩区被连出当漏极,而断开区域(场氧区域)利用N阱把中间的N+扩区连接到MOS管的漏极N+扩区上。此处N阱的作用用来限制ESD放电的瞬间峰值电流。另外在接触孔下有N阱结构,可防止ESD电流造成漏极与P型衬底间短路。利用工艺上场氧区域的间距大小即可做出不同大小的N阱电阻,这种电阻会影响到输出级的能力,但只要加大输出级的元件宽度即可使其恢复到正常的推动能力。

(2) 静电保护元件上的改进

集成电路在生产工艺上的改进必将会增加电路制造的复杂程度和成本,如果能开发出不须改变工艺的静电保护元件将具有更大的意义。低电压触发可控硅(Low Voltage Triggering SCR,简称LVTSCR)便是在单位面积下具有较高抗静电能力的保护元件。利用这种元件,CMOS集成电路的抗静电能力能够只占用很小面积便可达到较高的抗静电能力。

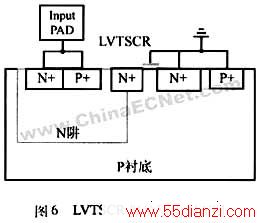

SCR元件的基本结构如图5所示。这种保护元件能在最小的布局面积下提供最高的ESD保护能力。但若只是简单的四层结构,则此SCR元件起始导通电压等于CMOS工艺下N阱和P衬底结面的击穿电压。由于N阱掺杂浓度较低,故其结面击穿电压在30~50V之间。具有如此高的结面击穿电压,使得SCR元件在ESD保护上需要加上第二级保护电路。第二级保护电路的目的在于提供较低电压时的ESD保护能力。但第二级保护电路会占用额外的布局面积,使得在PAD附近的版图结构变得复杂。常用的第二级保护结构为一个短沟道的NMOS元件,结构如图6所示。此改进SCR的起始导通电压等于短沟道NMOS元件的击穿电压,大约在10~15V左右。其原理是利用内嵌的短沟道NMOS元件发生击穿时,引发电流自N阱流向P衬底,因而触发了SCR元件的导通。为了防止该保护元件在正常工作情况下不会被导通,其内含的短沟道NMOS的栅极连到地上,以保持该NMOS元件在电路正常工作时是关闭的。这种LVTSCR元件的ESD能力得以大幅度提高且不需要额外的工艺处理步骤,但其缺点是不易设计,需要相当的经验才能够充分使得原本是缺点的寄生元件变为ESD保护的元件。

在进行集成电路I/O端口对电源和地的静电放电组合实验中,在对地正脉冲(PS)、对地负脉冲(NS)、对电源正脉冲(PD)、对电源负脉冲(ND)四种放电模式中,PS和ND模式最易导致集成电路损伤。在以前的设计中,LVTSCR只被安排在PAD地的放电路径上,故在先前的设计中仍欠缺对电源负脉冲保护的设计。

(3)电路改进方法

电路改进来提升集成电路的抗静电能力,主要是利用ESD放电的瞬间电压快速变化的特性,由电容耦合作用来使得ESD保护元件达到更好的保护作用。

1) 栅极耦合技术

在深亚微米集成电路工艺中,元件的ESD能力下降,为了提升集成电路的抗静电能力,在输入/输出PAD处的ESD保护元件或输出级元件都会做得比较大,经常布图为插指状。但在ESD时,由于相对位置和布线方向不同并非所有插指能同时导通。所以即使元件尺寸已做得很大也未必能如预期地提升ESD保护能力。为了克服上述问题图7、图8给出了利用电容耦合作用来使大尺寸集成电路的每一插指都能均匀导通的设计。图7为利用NMOS的扩散栅漏电容作耦合无件,另外一场氧元件加强了耦合电容的作用,当有正的ESD电压时,瞬间电压变化会导致NMOS栅极电压跟着上升,由于电容耦合作用,因为NMOS栅极上有耦合的正电压,故大尺寸NMOS元件的各个插指会一起进入击穿区,因此其ESD防护能力便可充分发挥。

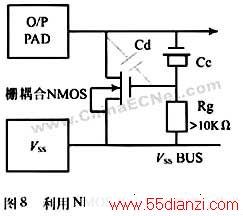

图8为电容耦合技术应用于输入级ESD保护的。种结构,栅耦合NMOS是ESD电流旁通用的元件,具有较大的尺寸。因应用于输入端,故其栅极须经电阻接地,该结构在正常工作时是常闭的。另有NMOS连结成电容,此NMOS是用来加强电容耦合作用。当有正的ESD电压作用在输入PAD上发生时,一部分正电压会经Cd与CC的耦合作用到栅耦合NMOS的栅极,此栅极电流会经Rg放电到地上,Rg的大小会影响到栅极电压的维持时间,GCNMOS因而可以达到均匀导通的目的,以提升其抗静电能力。

2)互补式栅极耦合技术

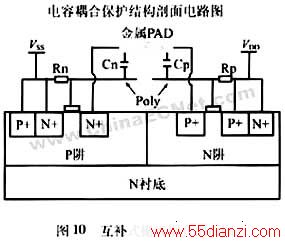

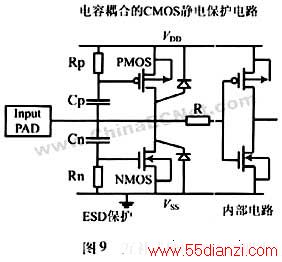

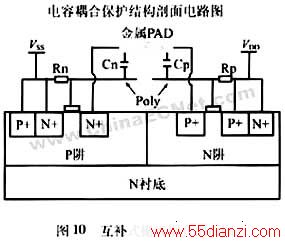

互补式栅极耦合技术是同时有对电源和地的栅极耦合NMOS元件。在任意I/O端口上的ESD放电有四种测试组合,所以ESD设计必须考虑这四种情况下的放电回路。选择合适的Cn(Cp)与Rn(Rp),能够提供有效的ESD保护而不影响电路的正常工作状态。图9和图10给出了此电路保护电路的原理图和剖面结构图,该耦合电容可以利用PAD与其下方的多晶层的寄生电容来实现,这样设计可以节省电路布局面积。

3)深亚微米集成电路的VDD对VSS防护技术

为提升该NMOS组件的ESD保护功效,图11为改良式的设计。在图中,一静电放电侦测电路被加入,用来控制该NMOS组件的栅极。当有ESD电压出现跨在VDD与VSS电源线上时,该静电放电侦测电路会送出一正电压把NMOS组件导通来旁通掉ESD放电电流。由于该NMOS元件是藉由其栅极控制而导通,而不是像栅极接地NMOS组件是靠崩溃才导通的,因此具有极低的导通电压。当内部电路组件尚未因ESD电压崩溃之前,该NMOS组件就早已导通来旁通ESD放电电流了。这导通的NMOS组件在VDD与VSS之间成一暂时性的低阻抗状态,因此跨在VDD与VSS之间的ESD电压能够很有效地被箝制住,不会再造成IC内部电路因ESD 而出现异常损坏的现象。利用此一改良式的ESD箝制电路,可以有效地防护脚对脚的ESD放电。当管脚对管脚ESD电压转变成跨在VDD与VSS电源线之间时,该RC控制的ESD侦测电路会因ESD的能量而偏压工作,并送出正电压到NMOS组件的栅极来导通该NMOS,ESD电流便经由这导通的NMOS组件而排放掉,因此IC的内部电路及寄生的SCR与BJT组件都不会因为ESD的过压而破坏。

本文关键字:暂无联系方式电路基础知识,电子学习 - 基础知识 - 电路基础知识