MOS���ɵ�·����:NMOS����ɵ�NMOS��·��PMOS����ɵ�PMOS��·����NMOS��PMOS���ֹ�����ɵĻ���MOS��·����CMOS��·��

PMOS�ŵ�·��NMOS��·��ԭ����ȫ��ͬ��ֻ�ǵ�Դ�����෴���ѡ�

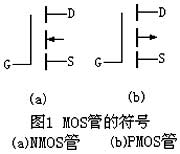

���ֵ�·��MOS���ɵ�·��ʹ�õ�MOS�ܾ�Ϊ��ǿ���ӣ����س���MOS����Ϊ��Դ���أ�����������ʡ�˹�Ƭ��������Ҽ��˹������ڴ��ģ���ɡ����õķ�����ͼ1��ʾ��

��1�����ĵ�

CMOS���ɵ�·���ó�ЧӦ�ܣ��Ҷ��ǻ����ṹ������ʱ���������ij�ЧӦ�����Ǵ���һ���ܵ�ͨ����һ���ܽ�ֹ��״̬����·��̬����������Ϊ�㡣ʵ���ϣ����ڴ���©������CMOS��·��������̬���ġ������ŵ�·�Ĺ��ĵ���ֵ��Ϊ20mW����̬���ģ���1MHz����Ƶ��ʱ��Ҳ��Ϊ��mW��

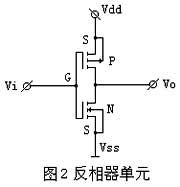

��2��������ѹ��Χ��

CMOS���ɵ�·����������Դ���С�������ϲ�����ѹ������CC4000ϵ�еļ��ɵ�·������3~18V��ѹ������������

��3�����ڷ���

CMOS���ɵ�·�����ߵ�ƽ“1”�����͵�ƽ“0”�ֱ�ӽ��ڵ�Դ�ߵ�λVDD����Ӱ�͵�λVSS����VDD=15V��VSS=0Vʱ��������ڷ�����15V����ˣ�CMOS���ɵ�·�ĵ�ѹ����ϵ���ڸ��༯�ɵ�·��ָ���ǽϸߵġ�

��4������������ǿ

CMOS���ɵ�·�ĵ�ѹ�������ĵ���ֵΪ��Դ��ѹ��45%����ֵ֤Ϊ��Դ��ѹ��30%�����ŵ�Դ��ѹ�����ӣ���������ѹ�ľ���ֵ���ɱ������ӡ�����VDD=15V�Ĺ����ѹ����VSS=0Vʱ������·����7V���ҵ��������ޡ�

��5�������迹��

CMOS���ɵ�·�������һ�㶼���ɱ��������ܺʹ������蹹�ɵı������磬�ʱ�һ�㳡ЧӦ�ܵ����������С����������������ѹ��Χ�ڣ���Щ���������ܾ����ڷ���ƫ��״̬��ֱ�������迹ȡ������Щ�����ܵ�й¶������ͨ������£���Ч�����迹�ߴ�103~1011Ω�����CMOS���ɵ�·����������������·�Ĺ��ʡ�

��6���¶��ȶ����ܺ�

����CMOS���ɵ�·�Ĺ��ĺܵͣ��ڲ��������٣����ң�CMOS��·��·�ṹ�͵������������жԳ��ԣ����¶Ȼ��������仯ʱ��ijЩ���������Զ��������ã����CMOS���ɵ�·���¶����Էdz��á�һ���մɽ�����װ�ĵ�·�������¶�Ϊ-55 ~ +125�棻���Ϸ�װ�ĵ�·�����¶ȷ�ΧΪ-45 ~ +85�档

��7���ȳ�����ǿ

�ȳ��������õ�·��������ܴ����������������ʾ�ġ�����CMOS���ɵ�·�������迹���ߣ���˵�·�����������������ݵ����ƣ����ǣ���CMOS���ɵ�·��������ͬ���ͣ��粻�����ٶȣ�һ���������50�����ϵ�����ˡ�

��8������������ǿ

CMOS���ɵ�·�еĻ���������MOS����ܣ����ڶ��������ӵ����������������ߡ�������䵼�����ܵ�Ӱ�춼���ޣ�����ر��������������켰��ʵ���豸��

��9���ɿ��Ժ�

CMOS���ɵ�·������ε��������½�ʱ����Կ��ƣ���������������½�ʱ��ĵ���ֵΪ��·�����ӳ�ʱ���125%~140%��

��10���ӿڷ���

��ΪCMOS���ɵ�·�������迹�ߺ�����ڷ����������ڱ�������·��������Ҳ���������������͵ĵ�·��������

��CMOS���ɵ�·�е�һ���������·——���������������ӵ�CMOS���ɵ�·������ɷ�������Ԫ��϶��ɣ�Ϊ��������CMOS���ɵ�·�Ĺ������̡�

����һ��P����MOS�ܺ�һ��N����MOS�ܻ������Ӿ�����һ��������ķ�������Ԫ��·�總ͼ��ʾ��ͼ2��VDDΪ����Դ�ˣ�VSSΪ����Դ�ˡ���·��Ʋ�����������������“1”Ϊ�ߵ�ƽ����“0”Ϊ�͵�ƽ��

ͼ2�У��������ѹVIΪ�͵�ƽ“0”��VSS��ʱ��N����MOS�ܵ�դ-Դ��ѹVGSN=0V��Դ���ͳĵ�һ���VSS������������ǿ�ܣ����Թ��ӽ�ֹ����P����MOS�ܵ�դ-Դ��ѹVGSN=VSS—VDD����|VSS—VDD|>|VTP|��MOS�ܿ�����ѹ������P����MOS�ܵ�ͨ�����������ѹV0Ϊ�ߵ�ƽ“1”��VDD����ʵ�������������ķ���ܡ�

�������ѹVIΪ��ƽ“1”��VDD��ʱ��VGSN=��VDD—VSS��������VDD—VSS��>VGSN����N����MOS�ܵ�ͨ����ʱVGSN=0V��P����MOS�ܽ�ֹ�����������ѹV0Ϊ�͵�ƽ“0”��VSS������VI��Ϊ�����ϵ��

������������֪���������ź�Ϊ“0”��“1”���ȶ�״̬ʱ����·�е�����MOS������һ�����ڽ�ֹ״̬��ʹ��VDD��VSS֮�����迹ֱ��ͨ·����˾�̬���ļ�С�������CMOS���ɵ�·����Ҫ���ص㡣

���ɵ�·������ܵ����ʷ�Ϊ�ԣԣ̺ͣãͣϣ������࣬�ԣԣ����ٶȼ������ãͣϣ��Թ��ĵͶ����ƣ����Уãͣϣӵ�·�������������Գ�ΪĿǰӦ����㷺�ļ��ɵ�·���ڵ���������ʹ�ããͣϣӼ��ɵ�·ʱ�����������Ķ���Ʒ˵�����й����ϣ��˽������ŷֲ����������⣬��Ӧע�����¼������⣺

��1����Դ����

1�� �ãͣϣӼ��ɵ�·�Ĺ�����ѹһ���ڣ��������֣�����Ӧ�õ�·�����ŵ�·��ģ��Ӧ�ã������������ԷŴ�ʱ����͵�ѹ��Ӧ���ڣ������֡����ڣãͣϣӼ��ɵ�·������ѹ������ʹ�ò���ѹ�ĵ�Դ��·�ãͣϣӼ��ɵ�·Ҳ�����������������ǹ����ڲ�ͬ��Դ��ѹ��������������迹�������ٶȺ����Dz���ͬ�ģ���ʹ����һ��Ҫע�⡣

2���ãͣϣӼ��ɵ�·�ĵ�Դ��ѹ�����ڹ涨��Χ�ڣ����ܳ�ѹ��Ҳ���ܷ��ӡ���Ϊ����������У���Ȼ�γ�������������ܣ�Ϊ��������·����������ѹ�£���Щ�����ܽԴ��ڷ�ƫ������������Ӱ�죬����������Щ���������ܵĴ��ڣ�һ����Դ��ѹ�����ѹ���Խӷ����ͻ�ʹ��·������

��2��������������

�ãͣϣӵ�·��������������ߣ���ѡ������������ǿ�Ļ����������֮�⣬���ɽ�ͬһ��оƬ����ͬ���·����������ߣ���ʱ����������ߵ��α�����Ϊ�����ŵ���������

��3������˵�����

1����������˵Ĵ������ãͣϣӵ�·������˲��������գ���Ϊ���ջ�ʹ��λ�������ƻ�����������ϵ�����⣬����ʱ�����迹�ߣ���������������ţ�ʹ��·��������������Ҳ�������դ����Ӧ���������������“��”�ţ�“���”�ŵĶ��������Ҫ�Ӹߵ�ƽ��“��”�ź�“���”�ŵĶ��������Ҫ�ӵ͵�ƽ������·�Ĺ����ٶȲ��ߣ�����Ҳ�����ر���ʱ������Խ������������ʹ�ö˲�����

2������˽ӳ�����ʱ�ı�������Ӧ������ʱ�������Ҫ�ӳ��ĵ��ߣ����������߱�Ȼ�нϴ�ķֲ����ݺͷֲ���У����γɣ̣����ر������һ����������ѹ�������ƻ��ãͣϣ��еı��������ܡ��䱣���취Ϊ������˴���һ�����裬 �ң��֣ģģ���������

3������˵ľ����������Ȼ���֣ãͣϣ�������п�����ı�����ʩ��������С�ĶԴ����ڴ洢������������ý����������ߵ�����ϰ�װ����Ҫ�����ײ��������ѹ�Ļ������ϻ���֯���С���װ������ʱ�����ߡ��DZ�������̨�Ⱦ�Ӧ���ýӵء�Ҫ��ֹ������Ա�ľ��������ɵ����粻�˴������������·����ֻ��ڽӴ����ɿ�ǰ����Ƚ�һ�µء����������߽�ֱ�������˹�����ʱ��ʹ�õ��豸�������ýӵء�

4�������źŵ��������½�ʱ�䲻����������һ�������������ٴ�������������ʧȥ�������ܣ���һ���滹����ɴ����ġ����ڣ����ȣ�ϵ�����ڣ������������ڡ����������Ҫ������ʩ���ش�������������������.

5���ãͣϣӵ�·���кܸߵ������迹����ʹ�������������š�����;������������Ϊ�˱����ãͣϣӹܵ������㲻��������һ�������ڲ�����˽��ж����ܱ�����·��

���У�ԼΪ����������������Ω�����뱣�����������ʹ�����������迹��һ���½��������ڣ�����Ω���ϡ�����Ҳ����·��Ӧ�ô�����һЩ���ƣ�

�������·�Ĺ����������ãͣϣӵ�·����˵ı��������ܣ��䵼ͨʱ��������һ��Ϊ���������ڿ��ܳ��ֹ���˲̬�����������������������ʱ��Ӧ�������뱣�����衣���磬������˽ӵ��źţ��������С�������ߺܳ�����������ݽϴ�ʱ���ڽ�ͨ�ضϵ�Դʱ�������ײ����ϴ��˲̬�����������ʱ��������뱣�����裬���֣ģģ������֣���ȡ��������Ϊ������Ω���ɡ�

�������źű����ڣ֣ģĵ��֣ӣ�֮�䣬�Է�������������ƫ�õ���������ջ�������ڹ��������ʱ�����밴���Ƚ�ͨ��Դ������źţ��ȳ����źź�ص�Դ��˳����в������ڰ�װ���ı����ӣ��β�ʱ�������жϵ�Դ���Է�Ԫ���ܵ�����ĸ�Ӧ��������

���Ĺؼ��֣����ɵ�· ��·����֪ʶ������ѧϰ - ����֪ʶ - ��·����֪ʶ

��һƪ����ѹ������·