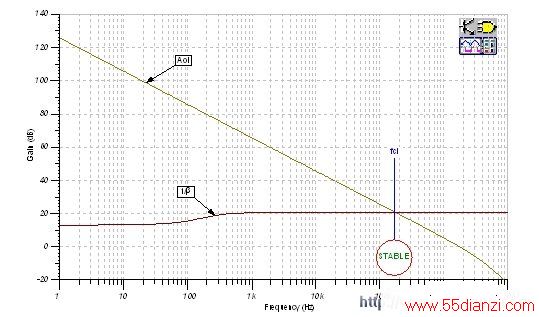

从图61中,我们可以看出,分析结果验证了我们所推算的最终1/β曲线。在环路增益为零的fcl处,推算的接近速率为20dB/decade。

图61:最终的1/β曲线:CMOS RRO。

图61:最终的1/β曲线:CMOS RRO。

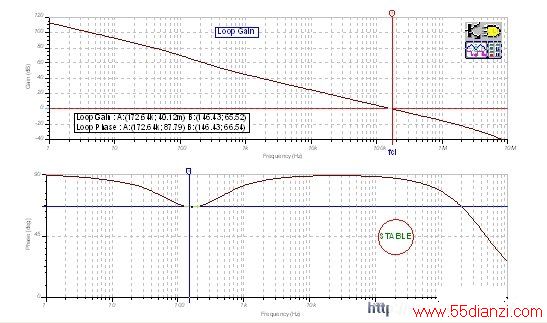

最终电路的环路增益相位曲线(采用FB#1和FB#2)如图62所示。相移从未下降至66.54度以下(出现在频率为146.43kHz的地方),因为,在fcl处(频率为172.6?kHz),相位裕度为87.79度。

图62:最终环路增益分析:CMOS RRO。

图62:最终环路增益分析:CMOS RRO。

我们将采用图63中的Tina SPICE电路对我们的稳定电路进行最后的检验-瞬态稳定性测试。

本文关键字:通道 电路基础知识,电子学习 - 基础知识 - 电路基础知识

上一篇:光敏电阻提供负反馈实现线性响应