我国靶场测量、工业控制、电力系统测量与保护、计算、通信、气象等测试设备均采用国际标准IRIG-B格式的时间码(简称B码)作为时间同步标准。B码是一种串行的时间格式,分为直流码(DC码)和交流码(AC码)两种,其格式和码元定时在文献[1]中有详细描述。本文介绍一种基于FPGA并执行IRIG-B标准的AC/DC编码技术,与基于MCU或者DSP和数字逻辑电路实现的编码方法相比,该技术可以大大降低系统的设计难度,降低成本,提高B码的精确性和系统灵活性。

在此,组合GPS引擎和FPGA,得到B码的编码输出,直接采用GPS引擎的100 pps信号触发输出B码的每个码元,利用从100 pps中恢复的1 pps信号提供B码的时间参考点。DC编码和AC数字调制均由纯硬件逻辑通过查找表实现,它能使每个码元的上升沿都非常精准,都可以作为百分秒的时间参考点,而计时链的预进位功能则保证了绝对时间的精确,不仅可以满足实时系统对时间同步,还可以实现多节点的数据采集严格同步,为分析和度量异步发生的事件提供有方的支持。

1 IRIG-B编码格式

IRIG标准规定的B格式码如图1所示,每秒钟发1次,每次100个码元,包含1个同步参考点(Pr脉冲的上升沿)和10个索引标记。码元宽度为10 ms,用高电平宽度为8 ms的脉冲表示索引标记,用宽度为5 ms的脉冲表示逻辑1,用宽度为2:ms的脉冲表示逻辑0。

如图1所示,交流码的载波是1 kHz正弦信号,幅度变化峰一峰值范围为0.5~10 V。调制比为U1/U0=1/6~1/2,即逻辑1是5个幅度为U1的1 kHz正弦信号,逻辑0是2个幅度为U1的1 kHz正弦信号,索引标记是8个幅度为U1的1 kHz正弦信号,其他时间是幅度为U0的1 kHz正弦信号。

2 系统方案

2.1 系统原理框图

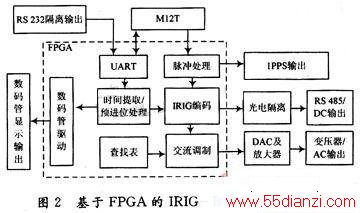

设计授时系统需要一个精准时基。在此利用精密授时型GPS引擎M12T作为系统时基,利用ALTEraFPGA检测M12T输出的百分秒(100 pps)同步信号和经串口输出的绝对时间信号,编码后输出到DC/AC接口模块,再输出到物理链路,系统结构图如图2所示。

上述系统首先实现了B码直流编码,而后在直流码的基础上实现交流调制,以得到交流码,同时提供恢复每秒脉冲数输出和隔离RS 232串行口输出且符合Motorola格式的时间码,以及数码管的时间显示。时间显示部分用FPGA实现比较简单,下文不再详述。

2.2 GPS授时模块M12T

M12接收器是Motorola公司优秀ONCORE家族中的新成员,广泛用于各类定位、导航、授时设备中,拥有全GPS行业内最快的初次定位时间和重捕获卫星的时间。M12T是针对GPS授时推出的定时精度更高的增强型产品。M12T具有12个并行通道,可同时跟踪12颗卫星,重捕获时间小于1.0 s。当拥有当前天历、位置、时间和星历数据时,首次定位时间TTFF<15 s。在位置保持状态时,定时精度(1 pps或100 pps)小于12 ns。

2.3 FPGA和DAC

FPGA采用ALTEra CycloneⅡEPC2C5T144,该芯片有4 608个LE,26个M4K,两个模拟锁相环。DAC采用单通道、单电源、自带基准的MAX5712。MAX5712是微型引脚,12 b解析度,片上精密输出放大器提供满摆幅输出。MAX5712用兼容SPITM/QSPITM/MICROWIRETM和DSP标准接口的3线串行接口。所有输入都兼容于CMOS逻辑,并经过施密特触发器缓冲,允许直接接光电耦合器。MAX5712含有上电复位(POR)电路,确保上电时DAC处于零电压输出状态。

3 时钟模块实现

3.1 基准时刻和索引脉冲的提取

要保证B码每个码元的上升沿时刻准确,需要100 pps的精确时基和pps的参考点。一般的做法是用pps作为基准,每个码元的起点由前两个秒脉冲的间隔等分得到。这种方法使用上一时刻来预测下一秒,每秒脉冲有抖动时会导致最后一个码元宽度不足或超过10 ms,这将无法利用B码来实现时间同步和数据等间隔同步的采集。本文直接使用M12T产生的100 pps信号作为每个码元的起始时刻,然后再从100 pps信号中恢复出1 pps。由于B码参考标记Pr=1 pps的上升沿,所以这种方法既保证Pr的准确性,又保证各个码元和索引标记时刻的准确性。在有等间隔同步数据采样要求的场合,可使用每个B码码元的上升沿校准本地时基,确保采样同步和时间同步。

M12T输出的100 pps信号(以下称PPM12)如图3所示,每个脉冲的上升沿时刻准确,周期10 ms,在pps的参考点,脉冲宽度为6~8 ms,其他时刻2~4 ms,脉冲宽度不是关注的重点。

B码的每个码元恰好与上述100 pps信号对应。首先在FPGA中构建一个模100的码元计数器MMH和一个高电平脉冲宽度检测器,通过下面的方法和步骤可以恢复pps。

(1)在PPM12信号的上升沿复位宽度检测器,高电平计时,在下降沿停止并输出Tb;

(2)在PPM12下降沿检查Tb,当6 msb<8 ms时,令MMH=1,否则执行下面的操作:

if MMH=99 then MMH=0

else MMH=MMH+1

(3)在PPM12信号的上升沿检查MMH,如果MMH=0,则当前脉冲的上升沿是参考点Pr,触发输出8 ms高电平脉冲作为pps信号,重复步骤(1)~(3),在PPM12信号上升沿检查MMH;如果MMH的个位为9或者MMH=0,则当前脉冲标记为索引脉冲,即输出8 ms高电平。

3.2 绝对时间获取

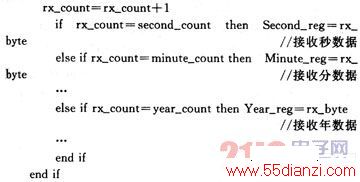

通过在FPGA上构建一个UART与M12T互连。为了简化FPGA对M12T的配置和输出时间的获取,将UART分成两部分设计,即发送模块txmit和接收模块rcvr。发送模块用一个M4K设计一个512×8 FIFO,在系统复位后的若干个时钟,利用一个状态机将M12T的配置数据写入FIFO;然后通过txmit模块配置M12T,配置结束后,UART模块将M12T的时间码转发到外部RS 232接口,同时可以转发外部接口的配置数据到M12T。接收模块采用寄存器模式,只接收M12T发来的绝对时间信息,这样后面的编码模块可以直接使用这些时间信息。做法如下:设计一个接收计数器rx_count,每接收一个字节计数器自加,并根据rx_count决定是否保存时间码。由于M12T每秒中发送一帧,故在检测到pps时复位该计数器。

www.55dianzi.com

if pps上升沿then rx_count=0

else接收到数据and rx_count

M12T在每个1 pps的上升沿过后送出当前时间,而FPGA通过UART接收到时间时,B码当前帧已经启动,据此形成的B码要等下一个pps参考点之后才可以发送,所以对接收的时间要进行预进位处理。

本文在FPGA预处理部分设计了一个RTC计时链,在每个1 pps的上升沿,计时链向上进位,编码模块从RTC计时链取绝对时间。从UART接收到新的时间后,如果该时间与计时链的值有差异,则将通过计时链的同步置数接口修正计时链的值。同时计时链负责把M12T的二进制时间转换成压缩的BCD码,还要根据当前接收到的年月日,计算当天是全年中的第几天,即IRIG-B码中的Day字段,而且在预加1 s和转换时间格式时,要注意闰年和月大和月小对Day字段的影响。

4 IRIG-B编码模块实现

4.1 IRIG-B DC编码模块

分析B码可以发现,秒的最低位出现在MMH=1处,分的最低位出现在MMH=10处,小时的最低位出现在MMH=20处,依次类推。按照图1,容易得出时间寄存器输出时刻和码元计数器MMH之间的关系。由于码元周期固定为10 ms,可以这样实现编码,定义一个模10的计数器MML和逻辑向量CMP(9 down to0)来表征一个码元在10 ms的状态。MML每ms加1,同时根据MML的值,选择CMP的一位更新输出状态,步骤如下:

(1)构建模10计数器MML,以及一个1 ms定时器;

(2)在PPM12信号的上升沿复位MML和1 ms定时器;

(3)1 ms定时器溢出时,MML加1;

(4)根据MML和CMP输出编码信号IRIG_B_OUT,即IRIG_B_OUT=CMP(MML);

(5)在PPM12的上升沿根据第3.1节所得码元计数器MMH重新加载CMP

算法VHDL描述如下:

本文关键字:编码器 仪表-仪器,电子制作 - 仪表-仪器

上一篇:第二代电流传输器的积分器设计