在上述VHDL编码的实现中,MSCLK为1 mS计数脉冲,同步于PPM12信号的上升沿。CMP的输出值由函数IRIG_B根据输入参数决定,若为0,则输出“0000000011”,对应2 ms;若为1则输出“0000011111”,对应5 ms,在索引脉冲和参考点Pr处,CMP取值“0011111111”,对应8 ms。而最终的编码输出IRIG_B_OUT在每个1 ms脉冲的上升沿,根据CMP(MML)的值决定为高或为低。

www.55dianzi.com

4.2 IRIG-B AC编码模块

4.2.1 数字调制原理

按照奈奎斯特抽样定理,只要抽样频率高于2倍信号的最高频率,则整个连续信号就能完全用它的抽样值来代表。使用抽样值构成的序列经DAC和低通滤波后即可恢复原来的连续信号。

若对频率为f的正弦波抽样N次(N>2f),并在T=1/f内通过DAC等间隔输出N次抽样值,则低通滤波后可恢复原始正弦信号。各个采样点值为:

Ck=Asin(ωkt)=Asin[ωk(T/N)] (1)

式中:ω=2πf;f为信号频率。则式(1)变为:

Ck=Asin[2πfk(T/N)]=Asin(2kπ/N) (2)

4.2.2 正弦查找表

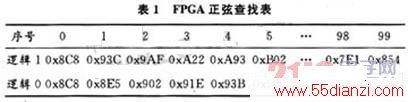

这里给出利用查找表实现交流数字调制的方法。在获得IRIG-B的直流编码后,将该信号导入到数字调制模块,即可获得交流编码。对正弦信号进行100次等间隔抽样,对式(2)使用实际的增益和直流偏移,可得式(3)。据此获得查找表。

Ck=Acsin(2πk/N)+A0 (3)

式中:N=100为采样率;k=0,1,2,…,N-1;Ck对应第k次抽样获得的值;A0为保证输出信号为单极性而设置的初始直流偏移;Ac为考虑调制比和DAC满幅度码值的系数。

由于交流信号频率为1 kHz,周期为T=1 ms,若在1 ms内将上述抽样值等间隔输出到DAC,即可获得1 kHz的调制信号。

本文使用MAX5712和单电源rail-rail运放AD8601构成滤波器。在MAX5712满幅输出时,C=4 095(12 bit DAC),选择调制比为1:5。综合考虑,在最大输出时,不能使DAC输出到达运放的上轨,最低输出时,DAC输出应高于运放的下轨,所以选取A0=C/2+200=2 248。对应逻辑0,Ac=461;对应逻辑1,Ac=1 844。根据上述原则计算出的正弦查找表如表1所示。

实际使用时,应根据使用DAC的解析度、运放的动态范围以及采样率及调制比确定上式中的参数。

4.2.3 DAC接口

实际使用时应根据DAC的不同,在FPGA中构建不同的数字接口。MAX5712需要在FPGA实现一个SPI接口,结构如图4所示。接口控制部分提供一个16 b写端口,可以接收数据。在写使能wren为高时,接口上的数据写入内部并行保持寄存器。在LDAC脉冲的上升沿,并行寄存器THR的内容写入移位寄存器,同时启动时钟逻辑。在输出时钟作用下,数据从Dout输出到DAC,在SPI_CS的后沿,DAC启动转换输出与当前编码相匹配的模拟量。

4.2.4 交流调制方法

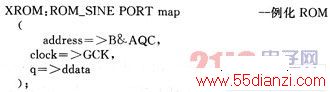

把按照第4.2.1节方法生成的正弦查找表生成ALTEra mif文件,再例化一个M4K ROM,使用上述文件作为ROM的初始化文件。建立一个周期为10μs的定时器和一个地址计数器。地址计数器和定时器在B码直流信号的变化沿复位,定时器溢出后启动地址计数器。或者把逻辑0对应的查找表放在ROM的上半部,如果把逻辑1对应的查找表放在ROM的下半部,且输入的直流B码信号作为地址的高位,则此时刻对应的ROM输出即为DAC的调制输出,ROM查找表VHDL的代码实现如下:

其中:B为来自编码器中IRIG-B的直流编码;AQC为地址计数器;ddata为输出到DAC的数字调制输出。由于查找表是按照对正弦信号做100次等间隔采样形成的,交流载波为1 kHz。所以AQC每隔10μs自加1,顺序输出100个编码值,在B码的每个变化边沿复位。

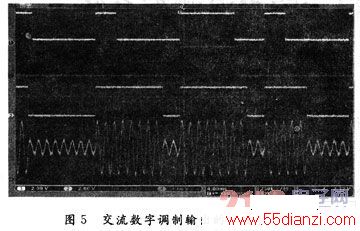

按上述方法设计的数字调制模块,用示波器测得输出波形如图5所示。

www.55dianzi.com

图5中,通道1(从上至下第一个信号)为M12T输出的100 pps信号PPMl2;通道2(从上至下第三个信号)为IRIG-B的直流编码输出信号;通道3(从上至下第二个脉冲)为从PPM12信号中恢复的每秒脉冲数信号;通道4(最下面的波形)为IRlG-B编码的交流输出波形。图5中示波器的触发点即为B码参考点Pr。

4.3 IRIG-B编码输出

4.3.1 直流码输出

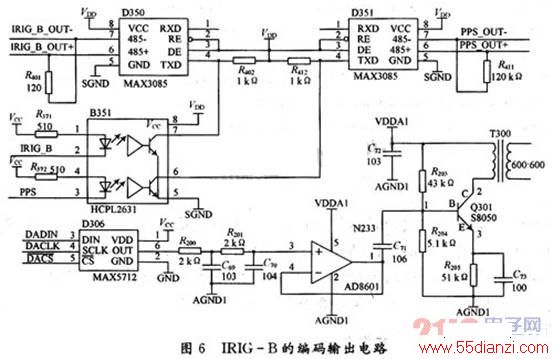

为了保证输出信号的边沿和抗干扰,将第4.1节得到的TTL电平B码信号和秒脉冲经高速光耦隔离,输出电路如图6所示。

图6中,输入信号IRIG_B为第4.1节所述FPGA编码模块输出的直流编码信号;pps为FPGA从M12T的100 pps信号中恢复的秒脉冲信号;D350和D351实现了TTL/RS485的电平转换。

4.3.2 模拟调制电压输出

IRIG-B编码的交流码输出电路如图6所示。将第4.2.3节所述数字调制信号通过DAC接口输出到MAX5712上进行D/A转换,经过AD8601滤除高次谐波后,再用电容耦合到由晶体管Q301构成的电压放大器中,然后经600:600的隔离变压器输出。

5 结 语

利用FPGA和M12T授时型GPS内核构成的IRIG-B编码模块采用M12T的100 pps信号触发IRIG-B编码器,使得编码输出的每个码元上升沿均与GPS模块严格一致,每个码元间隔严格相等,而且每个码元的上升沿均可作为同步参考点。利用FPGA的并发处理能力,使得系统实时性好。本文介绍的基于查找表的B码编码方法和通过查找表的数字调制方法具有占用资源小,设计简单,调制输出高次谐波小,信号边沿稳定等特点。

经过软件仿真和系统测试,本文实现的B码编码器中DC码参考点Pr和M12T GPS模块的pps参考点的时间误差小于20 ns,与绝对时间参考点之间的误差小于40 ns,AC码与DC码之间的延迟为100 ns。利用上述方法实现的模块已经成功地应用在我公司的通信管理机和同步时间服务器中,现场运行结果稳定、准确、可靠。

本文关键字:编码器 仪表-仪器,电子制作 - 仪表-仪器

上一篇:第二代电流传输器的积分器设计