在新一代电子电路设计中,随着低电压逻辑的引入,系统内部常常出现输入,输出逻辑不协调的问题,从而增大了系统设计的复杂性。例如,当1.8V的数字电路与工作在3.3V的模拟电路进行通信时,需要首先解决两种电平的转换问题,这时就需要电平转换器。

随着不同工作电压的数字IC的不断涌现,逻辑电平转换的必要性更加突出,电平转换方式也将随逻辑电压、数据总线的形式(例如4线SPI、32位并行数据总线等)以及数据传输速率的不同而改变。现在虽然许多逻辑芯片都能实现较高的逻辑电平至较低逻辑电平的转换(如将5v电平转换至3V电平),但反过来极少有逻辑电路芯片能够将较低的逻辑电平转换成较高的逻辑电平(如将3V逻辑转换至5V逻辑)。

另外,电平转换器,虽然也可以用晶体管甚至电阻,二极管的组合来实现,但因受寄生电容的影响,这些方法大大限制了数据的传输速率。

尽管宽字节的电平转换器已经商用化,但这些产品不是针对数据速率低于20Mbps的串行总线(SPITM、I2CTM、USB等)优化的,这些器件具有较大的封装尺寸、较多的引脚数和I/O方向控制引脚,因而不适合小型串行或外设接口和更高速率的总线(如以太网、LVDS、SCSI等)。

作者在设计数字系统时,要求考虑使用多个核心电压。存储器工作在1.8V.I2C和FP-CA器件的工作电压为3.3V,微控制器工作在5V。每种器件的时钟必须适应于其工作电压。

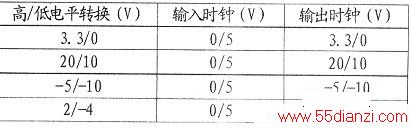

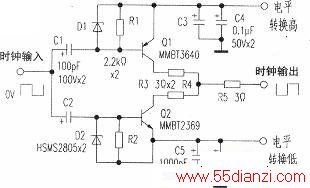

可以用附图中的电平转换电路,将输入时钟信号调整到适当的逻辑高和逻辑低电平,包括负电压。这种特|生对于需要负电压的器件很方便,如电荷耦合器件传感器。虽然电路的输出时钟,相对输入时钟呈180°反相,但这个反相并不影响器件的功能。

电平转换电路,包括快速切换的晶体管Q1和Q2。当需要选择电平转换为高和转换为低时,这实际是将直流偏置电压,连接到晶体管的射极,以匹配于所需要的输出高逻辑电平和低逻辑电平。C1、R1、D1、C2、R2和D2使Q1和Q2的基极电压保持在接近于射极电压。

由于存储器和电荷耦合器件传感器通常有高频时钟,因此可以通过选择Cl和C2防止低频噪声的通过。附图中的电路,用了一个20MHz的信号做测量,见附表,因此Cl和C2的值都采用100pF。当输入电压的时钟为低时.Q1导通而Q2关断,将输出电压的时钟驱动到电平转换的高电位;当输入电压的时钟为高时,Q1关断而Q2导通,将输出电压的时钟驱动到电平转换的低电位,即使该电位相对地为负。

由于电路有高的切换速度,元件引线要尽量短,以减少寄生电感,尤其是C3至C6与各自相应晶体管射极的接线,以及连接地或输出地回路。

本文关键字:暂无联系方式变换电路,单元电路 - 变换电路