在嵌入式系统设计中,PWM脉宽调制信号常常用来产生模拟信号。本文主要讲述如何利用MSP430系列微控制器的定时器输出PWM信号,产生正弦波、斜坡、直流以及交流信号等模拟信号。

1.概述

大多数嵌入式微控制器的系统均需要产生不同的模拟信号,通常采用集成或独立的DA转换器来实现。PWM信号常常也可以用来产生系统所需的模拟信号,包括产生直流和交流信号。本文以MSP430F149微控制器Timer_B模块的DA转换为例,可以产生上文提到的正弦波、斜波、直流电平以及在直流电平上增加正弦波产生的交流偏置信号。

2.工作原理

PWM信号为频率固定、占空比变化的数字信号,基本波形如下图所示。

如果PWM信号的占空比随时间而改变,那么信号经滤波后将输出幅度变化的模拟信号。因此通过改变PWM信号的占空比,即可产生不同的模拟信号。PWM信号实现DA转换(简称PWMDAC)的原理框图如下图所示。

T1公司的一些语言处理技术也通常采用PWMDAC方式实现。

2.1分辨率

PWMDAC的分辨率理论上即为定时器的计数器长度,通常该值被保存在定时器的CCRO寄存器中。PWM的最低有效位是定时器的一个计数值,而分辨率即为定时器所能计数的最大值,即Rcounts=Lcounts,其中Rcounts为计数器所能达到的最大计数值,也是就PWMDAC的分辨率,Lcounts为定时器的计数长度。例如,一个DAC转换分辨率为8-bit,则计数器的长度即分辨率为8bit或者为256。

通常,基于PWM定时器和滤波器的PWMDAC的分辨率等于将PWM信号用来产生DA转换的分辨率。此时,PWM信号的分辨率取决于计数器的长度和PWM计数器能实现的最小占空比。用公式表式为:Rcounts=L/C,其中L为计数器的长度,C为PWM计数器能实现的最小占空比;用比特分辨率表示为:![]() 例如,PWM计数器的长度最大为 512个,能实现的最小占空比为 2个计数值,则 PWM DAC 的分辨率Rcounts= UC =256,或者 Rbits=Log2

例如,PWM计数器的长度最大为 512个,能实现的最小占空比为 2个计数值,则 PWM DAC 的分辨率Rcounts= UC =256,或者 Rbits=Log2

2.2频率

通常PWM信号的输出频率等于DAC的刷新频率,因为可以将PWM占空比的每一次变化等效于一次DA转换的采样。

PWM定时器的频率取决于PWM信号的频率和所需的分辨率,表示为Fcolck=FPwm×2的N次方,其中Fdcck为PWM定时器频率,F则为PWM信号频率,即DAC的更新频率,n为DAC所需的比特分辨率。

接下来梅描述如何利用8-bitPWMDAC产生一个250Hz的正弦波和125Hz的斜波信号。采样频率为8kHz,每个正弦波周期采样32个值(16x过采样),每个斜坡周期采样64次(32x过采样1。即PWM信号所需的频率为8kHz,所需的PWM时钟为2.O48MHz。

设计中,PVVM信号的频率应高于正弦波频率或产生该信号的带宽,因为产生PVVM信号频率越高,所需滤波器要求越低,且越容易确定合适的滤波器。

2.3PWMDAC对MSP430的资源需求

本文以如何利用Timer-B和外部滤波器同步产生250Hz正弦波、125Hz斜坡和2/3VCC的直流电平为例,说明PWMDAC对MSP430的资源需求。

将Timer-B配置为16位的UP模式,计数器计数到CCRO寄存器时复位,即从0开始继续计数。CCRO寄存器赋值255,即提供计数器的有效长度为8-bitoCCR1寄存器和TBI输出用于产生正弦波信号,CCR2寄存器和TB2输出用于产生斜波信号,CCR3寄存器和TB3输出用于产生直流信号。每一个输出模式均选用PWM模式7,即PWM复位/置位模式。模式7中,当计数器值达到各自CCRx值时,输出复位(低电平)信号,当计数值达到CCRO时,输出置位(高电平)信号。当CCRx值变化时,则经滤波后输出的信号将相应变化。系统的SMCLK时钟可作为定时器Timer-B的计数时钟源。

所需MSP430微控制器其它资源包括:(1)32768Hz晶振;(2)片上DCO工作晶振为2.O48MHz;(3)SMCLK和MCLK晶振为2.O48MHz。当然,系统应用的复杂程度改变时,所需要资源也会不一样。

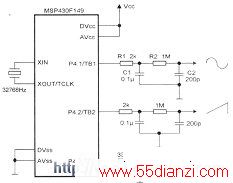

2.4电路设计原理本文设计的完整原理图如下图所示。

输出的交流正弦波信号的波形图如下图所示。

例如:输出一个正弦波,采用32采样频率产生。正弦波的频率为250Hz,所以每秒须采样250×32=8000次,而每次采样需要256次计数,所以计数频率采用8000×256=2.O48MHz。

斜波信号的产生是从最小占空比的PWM波经滤波后输出,然后逐渐增大占空比,直到输出最大电平值后,又重新开始从最小占空比的PWM波输出。

其中,直流信号及PWM信号波形图如下图所示。

直流电平的产生比较简单,可通过PWM信号占空比设置,该电平值不会发生变化,且直流电平值直接与PWM信号的占空比成比例。因此,只要PVVM信号的TB3占空比不变,当系统由RC网络滤波时,即为直流电平值。

2.5滤波器的设计本文产生的每一个信号的滤波器的原理图也如图3所示。用于产生交流信号的滤波器为一个简单的RC滤波器,设计简单且降低了系统功耗。设计中采样速率高于滤波器是必需的,通常建议DAC过采样至少为16x。

滤波器的截止频率为![]() 其中RC=RIC1=R2C2。当R2>>R1时滤波器的响应较好)但是如果截止频率很接近信号带宽边缘时,将导致相当大的衰减。为减小信号衰减,一般截止频率应大于信号带宽边缘,但是要远小于PVVM信号的频率。

其中RC=RIC1=R2C2。当R2>>R1时滤波器的响应较好)但是如果截止频率很接近信号带宽边缘时,将导致相当大的衰减。为减小信号衰减,一般截止频率应大于信号带宽边缘,但是要远小于PVVM信号的频率。

用于产生直流信号的滤波器仅用于存储电荷,因此单极RC滤波器即可实现。

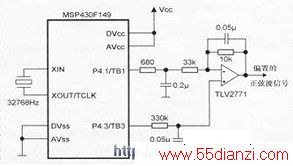

2.6盔加的DC和AC信号通过PWMDAC产生的信号可以叠加在一起,将2/3VCC电平加到正弦波上,产生一个偏置的正弦波信号的电路原理图如下图所示,

波形图如下图所示。

通过PWM输出可以很容易独立地调整交流和直流信号。

例如,正弦信号保持不变,直流偏置可以简单的通过改变PWM占空比产生所需的直流电平。当然,使用其它单独的滤波器和加法放大器也可以达到相同的结果。

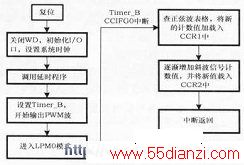

3.软件设计系统软件设计流程如图8所示。

系统复位后,首先禁止看门狗运行,设置I/0口并运行系统时钟;然后调用一延时程序,使32768Hz晶振稳定工作;设置Timer-B、CCR1和CCR2产生PWM信号,同时启动定时器。最后,为降低系统功耗,将MSP430Fl49设置为LPMO模式;开始工作后,通过CCIFGO中断唤醒CPU工作,中断完成后CPU再次进入LPMO模式。

3.软件设计系统软件设计流程如下图所示。

系统复位后,首先禁止看门狗运行,设置I/0口并运行系统时钟;然后调用一延时程序,使32768Hz晶振稳定工作;设置Timer-B、CCR1和CCR2产生PWM信号,同时启动定时器。最后,为降低系统功耗,将MSP430Fl49设置为LPMO模式;开始4.小结本文以MSP430Fl49微控制器和其Timer_B定时器模块输出PWM信号为例,也可以利用其它MSP430微控制器系列和Timer_A定时器模块产生不同的模拟信号。

本文关键字:暂无联系方式变换电路,单元电路 - 变换电路