���ۺϷ���LED����Ļ��ʾϵͳ����п��Ƶ�·�������Ʒ����Ļ����ϣ��ֱ�������Ե�Ƭ�����ɱ����������Ƕ��ʽ���������Ϊ���ƺ��ĵIJ�ͬ��Ʒ�����ʵ�ַ��������⼸�ַ������ص�����˱Ƚϣ���������Ӧ�������

LED�����ǹ�����Ϣ��һ����Ҫ��ʾ�նˣ����д���ĻLED������ʾ�������ೡ�ϵ���Ӧ�á�����Ļ��ʾ��������С��Ļ��ʾ�Ѷȸ�����Ϊ����Ļ��LED�����࣬����Ҫ�ڼ���ʱ����ˢ��ÿ���㣬���Ҫ����ɨ�����ʱ���dz��ߣ����⣬����Ļ��Ϊ��Ϣ��������Ҫý�飬�����ȶ��ԡ��ɿ����Լ�����չ��Ҫ�ܸߣ�ֻ����ƺ����Ŀ��Ƶ�·������������Ҫ������������LED����Ļ����п��Ƶ�·�ļ�����Ʒ�������Բ�ͬ�����Ҫ������˲�ͬ�Ľ��������

1LED����Ļϵͳ�Ĺ���ԭ��

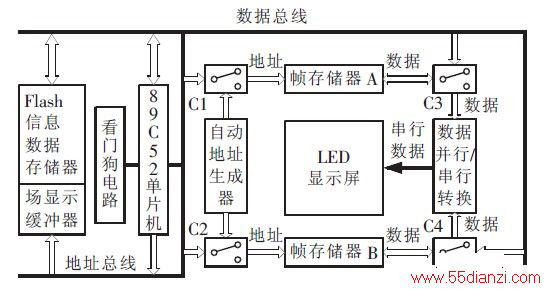

���͵�LED����Ļ��ʾϵͳ��Ҫ���źſ���ϵͳ�pɨ���������·�Լ�LED������ɣ�ϵͳ�ṹ��ͼ1��ʾ��Ŀǰ�����LED��ʾ������Ļ��Ʋ��õ���ģ�黯�Ľṹ�����Ļ�����Ԫ��LED��ʾ��Ԫģ�飬��Ļ��С����״�����ı䣬��ʾ���İ�װ��ά��Ҳʮ�ַ��㡣

ͼ1ϵͳԭ����ͼ

�źſ���ϵͳ����ϵͳ�p��Ƭ��ϵͳ�p��Z��Ƭ�����ӿ���ϵͳ�p�ɱ������������ϵͳ������ң��ϵͳ�p�������������ϵͳ�ȵȡ��źſ���ϵͳ�����������ɻ����LED��ʾ����������źţ�����������LED��ʾϵͳ�ĸ���������һ���ķֹ���ʱ��Э����������������·��Ϊ���������У���LED�ṩ��������������ɴ��벢����λ�Ĵ�������������������湦�ܵ���λ�Ĵ��������ɡ�

����ʾ���ݾ�������ϵͳ���Ƚ���һ������������λ�Ĵ��������棬Ȼ������ɨ���·ѡͨLED���еĵ�һ�У�����һ��ʱ�������ͬ��������ʾ�����У�ֱ�����һ֡����ʾ���ݣ����ѭ�������������Ӿ�������ԭ�����ܹ�ʵ��24f/s����ʾ���ܹ�������û�����Ե�ͣ�ٸУ��൱����Ӧʱ��Ҫ�ﵽ��40ms���¡���LED��ʾ������ܴ�ʱ�������������Ҳ�dz��Ӷ���������ʾϵͳ����Ӧʱ��������˸��Ϊ����Ӿ�Ч�������Է���������ʾ��

�ڸ��ٶ�̬��ʾʱ��LED�ķ���������ɨ�������ڵķ���ʱ������ȣ�����ͨ������LED�ķ���ʱ����ɨ�����ڵı�ֵ����ռ�ձȣ�����ʵ�ֻҶ���ʾ��

2LED����Ļ���Ƶ�·�����

���Ƶ�·������Ǵ���Ļϵͳ��Ƶĺ��ģ����Ƶ�·��ư����źſ���ϵͳ��ɨ���·��������·����ƣ����Ƶ�·�����һ�������ݴ洢�������ݻ��������������pͬ���������p��д�������p���ӿ���������ַ��������֡�洢���p����ѡ�������Ҷȵ���������λ�Ĵ����ȹ��ɡ�Ŀǰ��˵��LED��ʾ�����Ƶ�·��ƹ㷺��������������Ϊ����ƺ�����ʵ�֣�һ���ǵ�Ƭ������ϵͳ����һ���ǿɱ����������

2��1���ڵ�Ƭ���Ŀ��Ƶ�·��Ʒ���

���ڵ�Ƭ���Ŀ��Ƶ�·��Ҫ�����ַ�����һ����һƬ��Ƭ����Ϊ�����������ƺ�Э������Ļ������ʾϵͳ����ʾ��һ���Ƕ�Ƭ��Ƭ�����ɶദ����������һƬ��Ϊ��CPU��������Ϊ��CPUһ����ƴ���Ļ����ʾ��

ͼ2�Dz��õ�ƬCPU��ƵĿ��Ƶ�·����ʾ��ͼ����89C52��Ƭ����Ϊ���ƺ��ġ���Ƭ�����մ�PC����������ϢԴ����������ʾ���ݣ��洢��Flash�У�ͬʱ��RAM6264��Ϊ����ʾ����������ʵ�ֲ�ͬ��ʾ������ʽ��89C52�����л�����C1��C3��C2��C4ͬʱ��֡�洢��A��B����������ݵĶ�д�����������������ݽ��в���5����ת������ʾ��������ʾˢ�¡����У��Զ���ַ��������4���������������ɣ���������·�ṩ����ʱ�ӣ�����һ��M×N�����صĵ�ɫ������ˢ��Ƶ��Ϊ60Hzʱ������Ƶ��ΪM×N×60Hz���ڶ�Ҷȼ���ɫ����Ļ�������͵���ʾ��֮ǰҪ���лҶȵ�������ͼ���ɫ�ʣ������ݵĴ����ٶ�Ҫ����ߣ����õ�Ƭ�����ƿ������ٶ���������Ҫ��

ͼ2��ƬCPU���Ƶ�·�ṹʾ��ͼ

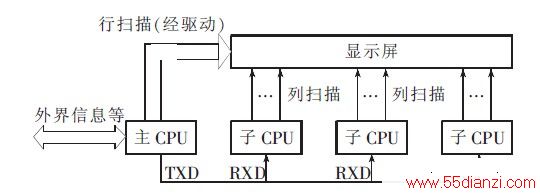

����Ŀǰ�ܶƬ����I/O�ھ߱���15mA���ϵ����������Ҽ۸�Ƚϱ��ˣ�����ڴ���Ļ�������Ҳ���öദ����������ϵͳ�Ļ����ص��ǣ�һ����ʾ�����ж��������������һ����CPU�Ͷ����CPU����ṹʾ��ͼ��ͼ3��ʾ����CPU��������ͨ�����ݲɼ��������ͨ�ŵȻ�ȡ��ʾ��Ϣ���ٴ������CPU����CPU��������ɨ��ͷ�����ʾͬ����Ϣ�ȡ���CPU������CPU��������Ϣ����ŵ��ڲ�RAM���У��ٸ�����CPU�����Ŀ�����Ϣѡ���ʵ���������ڽ�����ɨ�衣����ÿ����CPU����������ڵ����������Ϊm����ÿ��LED���������Ϊn����ÿ��оƬ����������LED�������Ϊm/n������ÿ����Ƭ������һ���>LED�飬�����ǿ��������չ��ͬʱ��������CPU�ĸ���������˵����ˢ��Ƶ�ʡ�

ͼ3��CPU���Ƶ�·�ṹʾ��ͼ

�ڶ����ʾ�Ĵ���Ļ����У����ַ�����Ϊ���룬�Բ�ͬ����ʾ������õ�������CPU������ɨ�裬��ͨ����CPU����ͳһ����ɨ�裬��Ȼ���Ƶ�·ʹ�õ�Ԫ���϶࣬����·�ṹ������ʵ�֡�

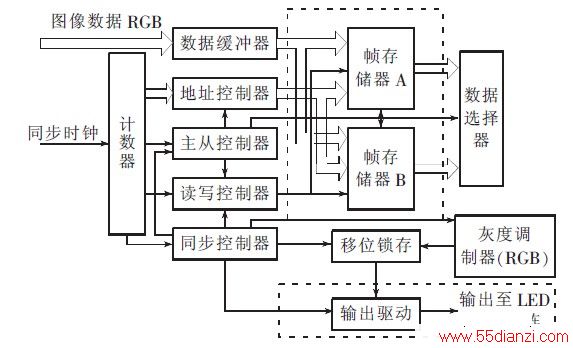

2��2����CPLD/FPGA�Ŀ��Ƶ�·��Ʒ���

Ƶͼ���ź�Ƶ�ʸߣ���������Ҫ��ʵʱ��������֮LED����Ļ��·���������൱���ӣ�����CPLD/FPGA��ƿ��Ƶ�·�����Լ�ϵͳ�ṹ�����ڵ��ԡ�ͼ4��CPLD/FPGA��ƿ��Ƶ�·��ԭ��ͼ������CPLD/FPGA���������е�ͬ�����ơ����ӿ��ơ���д���ƺͻҶȵ��Ƶȴ�����·�����˼��ɣ�ʹͼ�����ݴ�����Ϊ���٣�ͼ������ȶ�������ϵͳ�ṹ���գ������ɿ���������ߡ�

ͼ4CPLD/FPGA���Ƶ�·ԭ��ͼ

ͼ4�������������������ģ�����CPLD/FPGA���ʵ�֣������ӵ�Ӳ����·���ͨ�����������ȡ������ͼ2�ĵ�Ƭ�����Ƶ�·�Ա���������·�ṹ���Ը���࣬��·�������С���ɿ�����ǿ������Ҳ��Ϊ������CPLD/FPGA���Բ��д���������̣�����Ƭ���������˳����Ч�ʸ��ߣ������ˢ��Ƶ��Ҳ��֮��ߡ�

���⣬�ɱ����������Ƭ����ԴԽ��Խ�ḻ�����������ڲ���������RAM�飬��ALTEra��˾�Ƴ��ĸ��Լ۱�FPGA쫷�EP1C6Ϊ���������ڲ��ͼ�����20��RAM��ģ�飬ÿ������Ϊ4Kbit����ЩRAM���ͨ���������óɵ��˿�RAM����˫�˿�RAM��FIFO�ȣ�����ϵͳ�����ݴ�������Ҫ����������ƻҶȵ�����ʱ��ɫ�����ֵĻҶȵȼ�Խ�ߣ��ڱ�����ͬ��ˢ��Ƶ�ʵ�����£������ݵĴ����ٶ�Խ�ߣ���ʱ�����Խ�FPGA���ڲ�RAM�������ó�һ��˫�˿�RAM����Ϊ�Ҷȵ��ƵĻ��������ڶ�ȡ֡�洢���е����ݵ�ͬʱ�����ϴζ�ȡ�����ݽ��лҶȵ��ƣ����߽�����У��ӿ������ݵĴ������ʡ�����ʾϵͳ���ɶȺ��ȶ���Ҫ��ϸߣ�ͼ��Ҷȼ��϶�Ĵ���Ļ����У����ÿɱ����������ƿ��Ƶ�·�����㡣

����һЩ���Ƶ�·����Ʒ����ۺ������˵�Ƭ��������EDA���������õ�Ƭ��ʵ�����ݵĴ������洢��ͨ�Ź��ܣ�CPLD/FPGAʵ�����ݵĻҶȵ��ơ�ɨ����ʾ�ȹ��ܡ����ַ����Ե�Ƭ����CPLD/FPGA����ԴҪ���Ǻܸߣ���·���Ҳ��Խ����ף��ȱ�֤����ʾЧ�����ֽ�Լ����Ƴɱ���

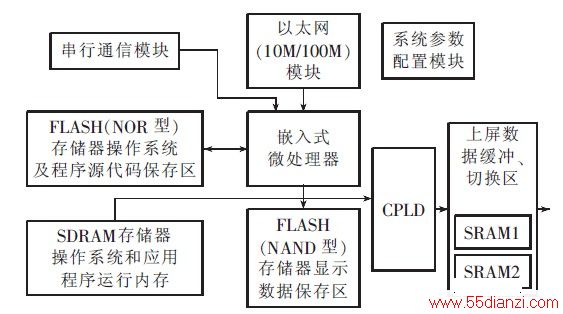

2��3Ƕ��ʽϵͳ�ڴ���Ļ����е�Ӧ��

����Ƕ��ʽ������������е�Ƭ����������ŵ㣺ָ��ִ���ٶȱ���ͨ��Ƭ����һ����������֧�ִ������Ĵ洢�ռ䣺����Χ�Ĵ洢���ӿ����ͣ���λ�����������ߣ���������ͨ�Žӿڣ��ر���Ƕ��ʽ����ϵͳ��ʹ�ÿ��Ը�Ϊ��Ч�Ĺ���ϵͳ��Դ�ķ��䣬ͨ�����Ч�ĵ����㷨��ʹ������Ӧ�ó������ƿ��Բ��ö�����ķ�ʽʵ�֣�����������ϵͳ�������ٶȺͿɿ��ԡ�����Linux��Ƕ��ʽϵͳ�Ŀ��Ƶ�·�����ͼ5��ʾ��

ͼ5����Linux��Ƕ��ʽϵͳ���Ƶ�·ԭ��ͼ

2��4����Ļ��ʾ����������

LED����Ļ������������Ҫ������#���п���������ʽ�����п���������ʽ�Լ�Ӧ�ø߶ȼ���ר��оƬ���������п���������ʽ�ǽ���ʾ������ͨ�����з�ʽ�������������·�����ص�����·���Ӽ����Է��㣬��Ԫ�Ŀɿ���Ҳ�ϸߣ����п���������ʽ��ѡ�õ�оƬ�У�MC4094��74LS595��9094�ȣ�������Ҫ���ʽϴ�һ����ô�������������������ɨ�������-���������ȿ��ƣ����ڴ��벢��оƬ�ɼ�����ΪLED��Ԫ�ļ����ṩ��֧�֡�

���Ĺؼ��֣�����Ļ ��ʾ��·-��ʾ������Ԫ��· - ��ʾ��·-��ʾ��