用PLL输出的核时钟即c0将rearrange模块输出的数据进行同步后送至LVDS_TX模块,时钟的连接方法如图7所示。在enable0信号有效时将数据输入至LVDS模块,LVDS_TX模块输出的24位数据输入给2个DA(I、Q),低12位为I路,高12位为Q路,并将输出640 MHz同步时钟送至DA。此时LVDS模块内仍可以调节输出数据和输出时钟的相位,但只剩下2个相位值可以调节,即0°和180°。

4 实验结果及分析

实验中由DSP分别发送100 MHz和225 MHz的正余弦波形数据至FPGA,经过双口RAM和LVDS_TX模块发送至AD9735,并从示波器上观察DA的输出波形。

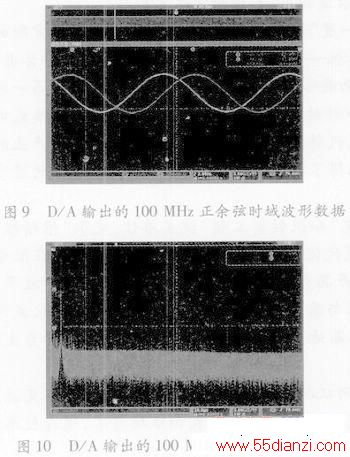

实验中c0相偏为-45°,sclkout0为-180°相偏。由DSP首先发送的是100 MHz的I、Q波形数据,AD9735的输出波形在示波器上显示如图9所示,其频谱如图10所示。

在100 MHz时,其杂散抑制可达-41.6 dB。

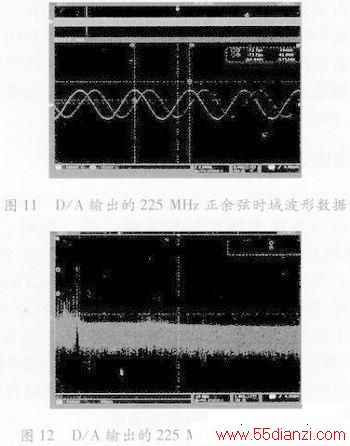

再发送225 MHz的I、Q波形数据,输出波形及频谱如图11和图12所示。

在225 MHz时,其杂散抑制可达-36.8 dB。

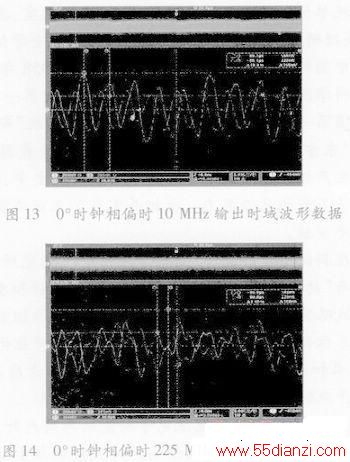

以下时钟相位的偏移对数据的影响,将c0和sclkout0相偏设置为0°。

仍由DSP发送100 MHz的I、Q波形数据,输出如图13所示,可以看出数据质量变差。

如图14所示,DSP发送225 MHz的I、Q波形数据的情况。

从图中看出,在225 MHz时时域波形质量较差,DSP发送的数据已是不能正确读出。可以看出在高速数据传输时,数据和时钟的同步很重要,正确调整时钟数据的相偏才能保证数据的正确传输。

由实验结果可以看出,在正确的时钟相位下,波形数据以640 Mbit·s-1的数据率正确的送至DAC,波形和频谱质量良好,通过LVDS_TX接口模块的应用,简单方便地实现了高速数据接口电路并输出高速LVDS信号,解决了高速时钟与数据的同步问题。

5 结束语

LVDS接口技术的优越性能使其在大型高速数据处理传输系统中的应用越来越广泛。介绍了基于FPGA的LVDS_TX模块在DAC系统中的应用,实现了高速LVDS数据的传输,应用时应要注意:LVDS并串转换时,数据bit位的顺序问题,正确相应的输入数据排列才能得到正确的输出数据,同时,无论是使用LVDS模块内部时钟还是外部时钟,都要注意时钟数据相位的正确调整,以便使数据与时钟准确对齐同步,从而得到正确良好的输出数据波形。

本文关键字:接口 接口电路,单元电路 - 接口电路