为让广大喜欢单片机学习的爱好者.有更多学习和应用对比的机会,下面详细介绍利用AT89C51单片机制作电子时钟,给大家提供可靠成功的电路和驱动程序。

一、电子时钟的实现形式

电子闹钟既可以通过纯硬件实现,也可以通过软硬件结合实现,根据电子时钟中核心部件——秒信号的产生原理,通常有以下三种形式:

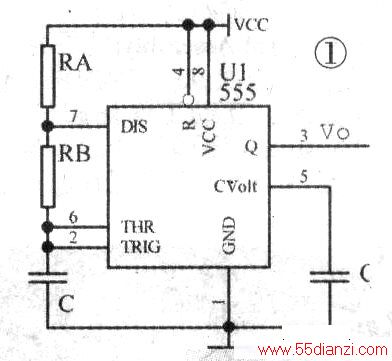

1.555时基电路的实现形式

采用NE555时基电路或其他振荡电路产生秒脉冲信号,作为秒加法电路的时钟信号或微处理器的外部中断输入信号,可构成电子钟。由555构成的秒脉冲发生器电路见下图。输出的脉冲信号VO的频率F=1.443/(RA+2RB)xC,可通过调节这3个参数,使输出vo的频率为精确的1Hz。

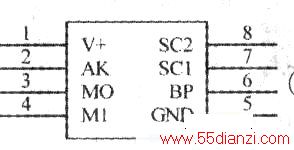

2.采用石英钟专用芯片的实现形式

采用石英钟专用计时芯片实现的电子钟.具有实现简单、计时精度高的特点。石英计时芯片(简称“机芯”)比较多,常见型号的有STP5512F、SM5546A和D60400等。现结台康巴丝石英钟常用的5512F型为例作一简单介绍。利用5512F的2秒输出信号作为秒加法电路的计数脉冲,可实现电子时钟。5512F的引脚图如下图所示。

3.采用基于微处理器的实现形式

利用微处理器的智能性,可方便实现具有智能的电子钟。由于微处理器均具有时钟振荡系统,利用系统时钟借助微处理器的定时/计数器可实现电子钟功能。虽然,系统时钟的误差较大,电子钟的累积误差也可能较大,但可以通过误差修正软件加以修正。

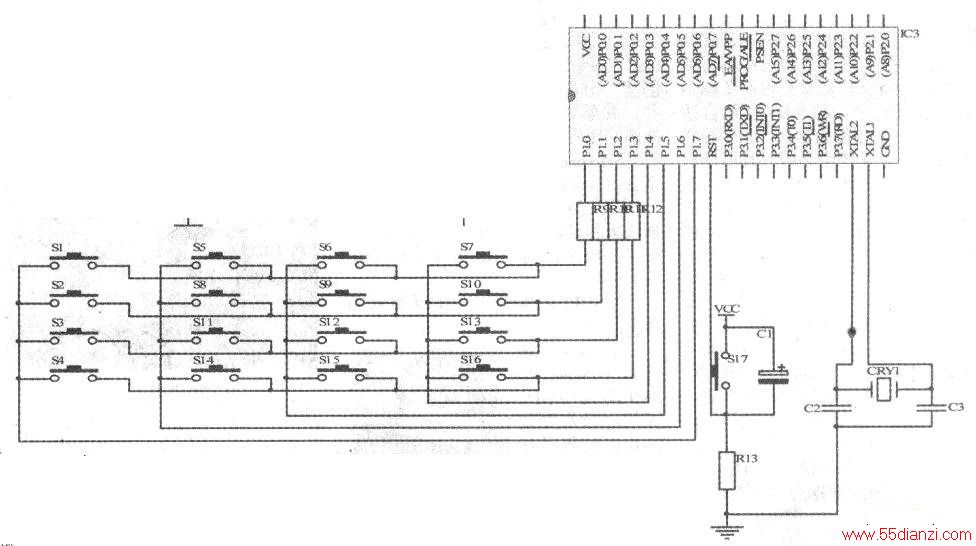

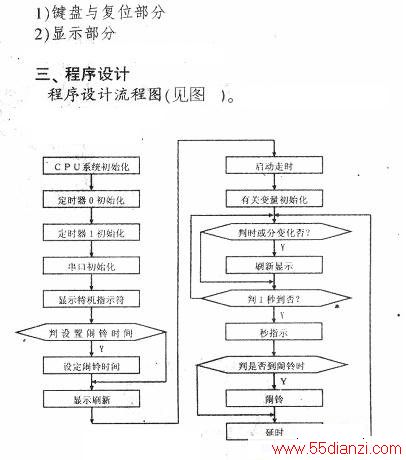

二、制作设计原理图

1.电子时钟的主电路设计

电子闹钟的主电路主要涉及到微处理器电路和按键按钮电路。主机的设计具体地说有:1)系统时钟电路设计:2)系统复位电路设计:3)按键与按钮电路设计:4)闹铃声光指示电路设计。以下分别讨论:

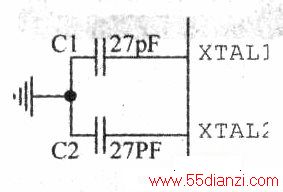

1)系统时钟电路设计

系统时钟电路的设计如下图。对于时间要求不是很高的系统,只要按图进行设计就能使系统可靠起振并稳定运行。但由于图中的C1、C2电容起着系统时钟频率微调和稳定的作用,因此,在本闹钟系统的实际应用中一定要注意正确选择参数(30±lOpF),并保证对称性(尽可能匹配),选用正牌厂家生产的瓷片或云母电容,如果可能的话,温度系数要尽可能低。实验表明,这2个电容元件对闹钟的±走时误差有较大关系。

2)系统复位电路设计

智能系统一般应有手动或上电复位电路。复位电路的实现通常有两种方式:1)RC复位电路:2)专用P监控电路。前者实现简单,成本低,但复位可靠性相对较低:

后者成本较高,但复位可靠性高,尤其是高可靠重复复位。但考虑各方面因素采用RC复位方式。

3)RC复位电路

本系统采用的是这种复位方式。RC复位电路的实质是一阶充放电电路,现结合下图说明这种复位电路的特点。系统上电时该电路提供有效的复位信号RST(高电平)直至系统电源稳定后撤销复位信号(低电平)。理论上说,51系列单片机复位引脚只要外加2个机器周期的有效信号即可复位,即只要保证t=RC>2M(机器周期)便可,但实际设计中,通常取C1为10μF以上,R1通常取10kΩ左右。实践发现R1如果取值太小,例如1kΩ,则会导致RST信号驱动能力变差而无法使系统可靠复位。

2.系统整个设计原理图

4)按键电路设计

按键与按钮电路设计中关键要考虑的就是按键去抖动问题(简称“去抖”),一般有硬件去抖和软件去抖两种方式。过去硬件去抖电路通常采用分立元件或触发器实现,目前市场上已有硬件去抖专用接口芯片,例如:MAXIM公司MAX6816—6818,均为单电源供电,电压为+2.7—5.5V,分别为单输入、双输入和八输入,输出端具有欠压锁定功能。这里考虑到系统的硬件简化和成本没有采用硬件去抖,而采用软件去抖。

其中,引脚⑦、⑧为钋接晶振及振荡电路,引脚①接电源正极,电源为1.5V,引脚③、④原为指针用步进电机线圈的输出驱动,这里可用③脚作为脉冲输出,频率决定于外接晶振的频率。

上一篇:280时钟电路