设计思想:

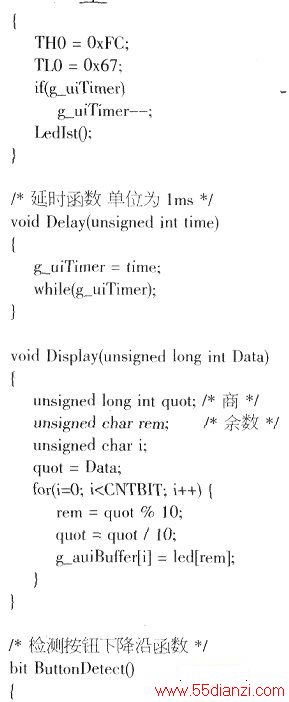

(1)使用定时器TO配置为一个1毫秒的定时时间做为时间基准,在TO中断里进行延时时间的精确定时。

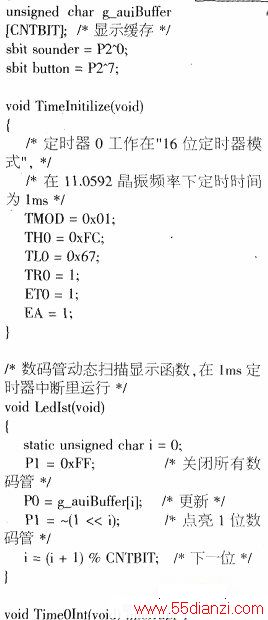

(2)在定时器TO中断里实现数码管的动态扫描显示。因为是用中断实现的动态扫描显示,所以每一位数码管的显示时间是一样的,不会产生显示明暗不稳的情况。

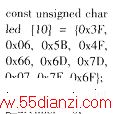

(3)每个数码管使用一个字节作为显示缓存,用于存贮动态扫描显示时的数据,在定时器TO中断里不进行数据转换,可减少定时器TO中断服务函数的实际执行时间,从而留出时间给CPU执行其它代码。

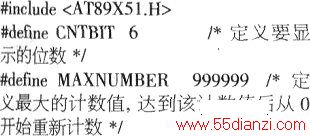

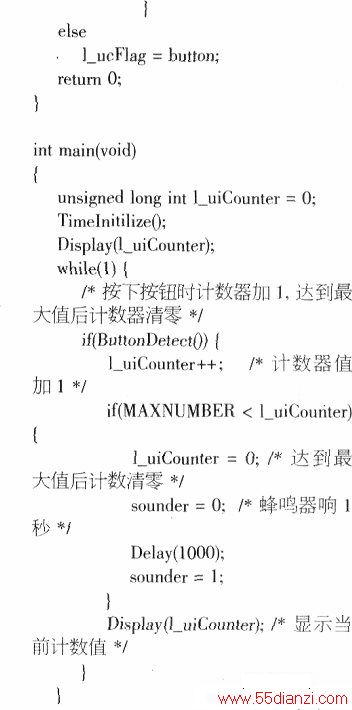

(4)使用一个“unsigned long int”类型的变量对外部按钮信号(或其它脉冲信号)进行计数。对于51单片机,“un-siWed Iong int”类型的数为32位,最大十进制数为“4,294,967,295”,即最大可以计十位数。如果使用“unsigned int”类型的变量,其最大十进制数为“65,535”,即最大可以计五位数。

(5)可以简单的修改程序实现减计数;可以简单的修改程序实现脉冲的下降沿计数或上升沿计数或两边沿计数:

可以简单修改程序更改计数器的最大计数值,到达最大值时自动从0开始计数:

可以简单的修改程序实现对多个外部脉冲信号进行计数。

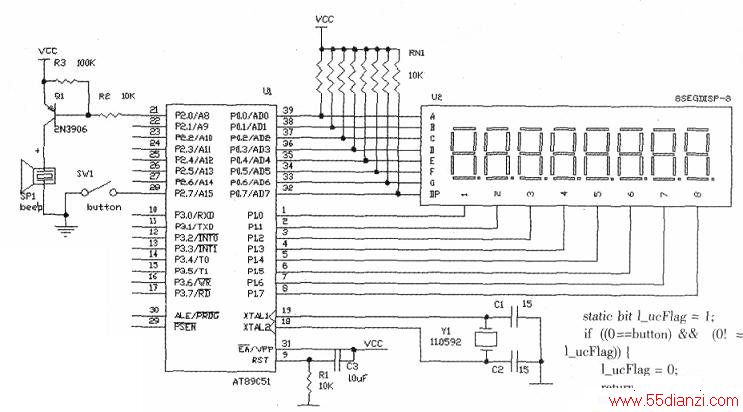

程序代码和电路图如下。

本文关键字:计数器 计数-倍频分频电路,单元电路 - 计数-倍频分频电路

上一篇:采用HT1350构成的脚步计数器