贝塞尔低通滤波器具有线性相位响应,通带无纹波、阻带单调衰减,适合时域应用。巴特沃思低通滤波器在通带内具有最平坦的频响,阻带的单调衰减也比贝塞尔滤波器陡峭,但相位响应随频率非线性变化,这使得巴特沃思低通滤波器非常适合基于幅度的应用。而椭圆低通滤波器具有接近平坦的通带响应和极为陡峭的阻带衰减,是基于幅度的抗混叠应用的最佳选择。

设计和实现连续时间有源滤波器非常具有挑战性,需要使用多个高性能运放和精度很高的无源器件。设计挑战包括如何选择最优的滤波器架构,还需要使用专用的滤波器计算软件2。另一个简单的方法是使用高度集成的SCF (开关电容滤波器),SCF可以大大减少外围 元器件 数目,使滤波器调谐十分简单,并可降低系统功耗。本文通过分析如何实现一个连续时间滤波器和一个SCF来说明其在性能和复杂程度上的不同。

如上所述,贝塞尔滤波器的特性使其非常适合时域应用,因为它们在示波器/分析仪这类测试应用中几乎没有失真。但设计者通常需要构建更高阶的贝塞尔滤波器(这意味着比巴特沃思或椭圆滤波器的极点更多)来实现足够大的阻带衰减。

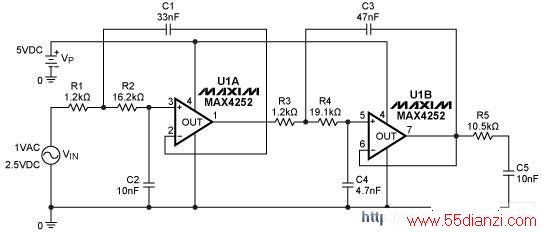

图1所示原理图为5阶、1.0kHz、低通贝塞尔滤波器,设计基于Sallen-Key架构,为减少元器件数目进行了优化,使用精度为1%的标准 电阻 和精度为5%的标准电容。为确定外围元件值,使用了滤波器设计软件 FiLTEr Pro?,并用PSPICE仿真工具进行了验证。

图1:两个运放和多个无源元件构成5阶、1.0kHz、低通贝塞尔滤波器。

许多情况下,输入和输出RC滤波器还需要一个额外的运放作缓冲,尤其是当信号源阻抗较高(大于几百欧)或滤波器输出的下一级输入阻抗过低(低于几百kΩ)时。

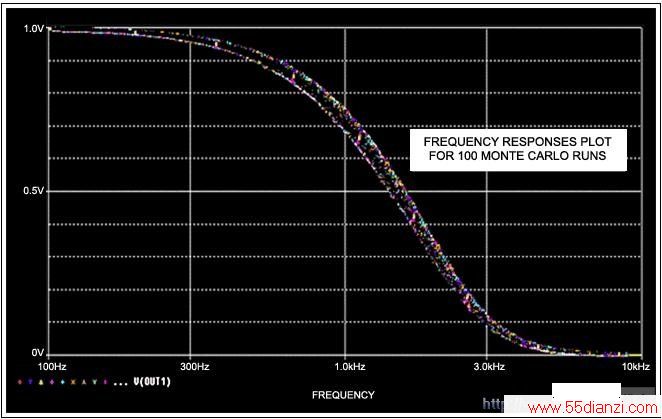

贝塞尔滤波器的SPICE仿真结果如图2所示,该频响图是同一滤波器进行100次Monte Carlo仿真计算的结果。SPICE 仿真器 通过在标称容限范围内随机改变外围元件值模拟器件的差异,仿真结果揭示截止频率会在fC = fIN -3dB ± 0.6dB范围内变动,这是电容和电阻值在标称容限内变化引起的。

本文关键字:滤波器 滤波-陷波电路,单元电路 - 滤波-陷波电路