(2)SMBus Timeout机制

SMBUS(System Management Bus),是1995年Intel公司提出的,最初设计应用于移动PC和桌面PC系统中的低速率通信。它与I2C总线电气及协议定义上类似,但在速率、超时错误、逻辑电平和总线协议上有所区别。DS4830主机I2C总线模块是使用兼容I2C总线协议,并引入SMBUS超时错误功能,使用一个30 ms的定时器,当总线SCL低电平超过这个时间后,触发TIMEOUT中断,以释放I2C总线,避免I2C总线的锁死。由于各种公司的I2C总线兼容协议可能存在一些差异,各种时序,包括一些非法或错误的时序都有可能在总线上出现,所以使用TIMEOUT机制来避免I2C总线死锁是相当有效和实用的。DS4830使能TIMEOUT功能,通过I2CCN_S(M)控制寄存器的SMB_MOD置位来实现。

结论

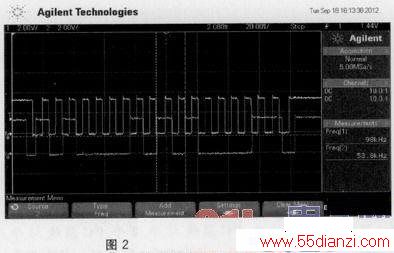

本文通过介绍DS4830相应主从I2C总线模块接口的寄存器,利用IAR编译环境实现了I2C总线从器件操作,并满足SFF-8472协议对多从机地址的要求。系统的上位机发出各种常规的I2C总线读操作及写操作均正常。该方法已应用于SFP+ZR、QSFP产品中,并得到客户系统验证,I2C总线可靠、稳定。

本文关键字:暂无联系方式总线技术,电子知识资料 - 总线技术