IMFT使用的先进工艺可以显著地改变消费电子产品的设计和使用方式。这些高密度、高性能闪存器件使得Intel支持的ROBSon闪存缓存技术以及混合SSD/HD系统(受到微软、Sandisk和希捷的支持)得以实现。这些技术很可能出现在那些需要大量存储器的产品中,例如台式电脑和笔记本电脑。微型MLC NAND闪存器件可以存储大量的数据,这些器件不需要供电就能保持数据。因为闪存器件中没有可移动的部件,因此它比硬盘更能承受震动,最终有可能替代硬盘。这种坚固性非常适合移动应用,特别是汽车应用,比如GPS导航系统以及高端汽车娱乐系统。

采用混合HD或Robson闪存缓存实现的闪存的数据访问速度可以比传统的USB闪存盘快100倍,这一点有助于提高那些蜂窝电话和PDA等移动设备的移动性和功能性。包括U盘、MP3播放器、数码相机、导航系统以及数据刻录机在内的其它产品也必将从这些新一代闪存器件中获益。

如果是从闪存而不是从硬盘中加载,典型的微软Word文档的打开时间将不到十分之一秒 (即使是非常大的文档也不会超过5秒),而Windows XP的启动时间也不会超过15秒钟,而且还具有将所有移动部件用一个元件整体替代的固有可靠性。闪存的优点还不止这些,就拿数码相机存储卡来说,如果每天读写约1000幅照片,那么在需要更换之前可以使用的时间将长达7年。因此这种卡在真正寿终正寝之前还有机会在新的相机中重复使用。

从50纳米启程

为满足英特尔-美光合作项目的高预期,IMFT必须缩小与关键竞争者东芝和三星公司之间的技术差距。SEMIconductor Insights公司在2006年9月份的报告中详细指出,IMFT为实现在2006年的第三季度发布50纳米、4Gb SLC闪存产品煞费苦心。从分析报告中可以明显看出,IMFT放弃了它的两个母公司采用的传统策略。美光从一个成本和制造创新者转变为了前沿技术的创新企业,这个变化是非常巨大的。

但是IMFT并没有完全弥合上述差距,还差那么一点点。竞争对手东芝公司一直以来使用MLC技术优化存储器密度,能用8Gb、70纳米闪存工艺技术实现高达56.5Mb/mm2的存储器位密度。IMFT的4Gb SLC闪存器件即使采用其先进的50纳米技术,也不能达到东芝的41.8Mb/mm2密度。

IMFT公司的4Gb器件采用三层金属、三种聚合物、50纳米CMOS工艺制造。尽管美光公司很早就以DRAM互连工艺实现了铜连接,但IMFT在金属层2和3中采用了一种更保守的铝互连工艺,而金属层1则采用了创新的钨过孔优先的双镶嵌(dual damascene)技术。

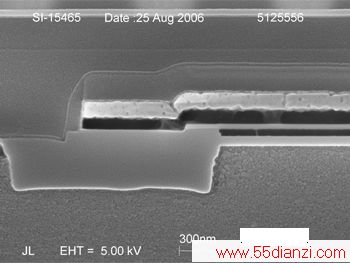

用于4Gb器件的特殊浅沟道隔离工艺可以用来实现具有交互多晶硅电容结构的三栅氧工艺技术。这是一种创新的隔离方法:在有效区域硬掩膜/STI抛光阻隔层形成之前形成栅极电介质。IMFT使用了多晶硅硬掩膜(类似于氮化物顶层)替代传统的氮化硅,因此与传统方法的差别更加扩大。

在经过STI蚀刻、填充和平整后,就形成了与隔离表面共面的内嵌多晶硅层。在厚的高压氧化物生长的区域,这种多晶硅层被用作多晶硅电容的低极板,并且具有高质量的CMP完工界面。屏蔽式清除随后沉积的ONO电容电介质即可提供第二个聚合物层到低位电容极板的接触区域。在晶体管栅电极将被形成的区域中, ONO层将被完全清除掉。

16Gb超级大转变

IMFT的“下一代”50纳米16Gb MLC工艺实际上是一种不严格的“近似40纳米”的工艺技术。与前一代技术一样,这种器件也是采用三层金属、三种聚合物工艺制造的。粗看起来,这种宣称的50纳米16Gb MLC器件并无什么特别的,甚至感觉它推出得迟了(想一想自从4Gb SLC闪存产品推出以来过了多长时间吧)。但是,这只是表面现象,真正要理解这种产品和早期的50纳米产品有多大的差异,必须要详细了解器件的内部。

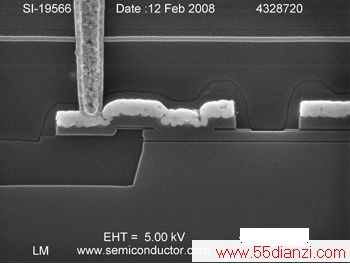

首先,IMFT的工程师已从基于铝的互连技术转向了铜互连技术。这种新的工艺将更容易地调整金属化层来适应接近40纳米的设计。使用钨过孔优先的双镶嵌技术形成的金属层1可以很简单地从4Gb版本转移到新的16Gb闪存器件;我们可以看到金属层1是否会在40纳米工艺时第二次用到。

IMFT还修改了浅沟道隔离的集成顺序。这种修改为存储器阵列中的有效区域间距提供了可缩放性(这对于IMFT推动下一代工艺节点很关键),SemIConductor Insights对此有很详细的研究。有趣的是,尽管这种修改允许缩放,但在这个顺序中的某些步骤看起来并不具有任何技术优势。有人不禁会认为,这种方法是否是为了回避其他闪存提供商拥有的STI工艺顺序。

最后,这个器件上几乎20%的阵列聚合物宽度减少应该能降低阵列中的电容性耦合,并改善整体的功率和速度性能。这将进一步确定针对下一代技术节点的工艺,特别是如果低k值材料被用来进一步降低存储器阵列中的耦合。

揭开表象

东芝和IMFT的16Gb MLC NAND闪存器件背后具有不同的细节。东芝在其推出的16Gb、56纳米MLC器件上实现了令人印象深刻的94.5Mb/mm2存储位密度;但是IMFT在其16Gb MC器件上实现了98.7Mb/mm2的密度,已经超过了东芝的存储位密度,并且几乎与竞争对手三星公司的51纳米、16Gb NAND器件的101.7MB/mm2存储密度相当。

再加上IMFT的浮栅宽度已经降低了20%,你就不会意外地看到明年初他们推出采用对目前50纳米工艺稍加修改的新工艺开发的样片。从更大的角度来说,每次技术迁移都能让我们进一步接近更高性价比的固态驱动器。当我们实现超越时,必将出现新的消费产品,并产生对半导体技术领域更高容量的需求。过去几年中我们在半导体行业获益良多,我非常期待这样的技术进步。

图1:多晶硅电容结构。底部的黑线是低位多晶硅板

图2:16Gbit闪存的多晶硅电容结构,图中显示了低位板接头。IMFT的4G、16Gbit NAND闪存

图3:IMFT的16Gbit MLC闪存的金属层2和层3采用铜双镶嵌工艺,金属层1采用钨双镶嵌工艺

本文关键字:技术 主板-硬盘-存储-插卡,电子知识资料 - 主板-硬盘-存储-插卡

上一篇:非易失数据存储器防误写措施