经过如上的防冲突过程,射频场内的射频卡将可以逐一被识别并进行数据交换。

2.3 串行通信程序

系统使用PC机作为上位机,读卡器作为下位机。上位机与下位机之间的通信采用基于RS-232-C的串口通信。RS-232-C是一种串行通信总线标准,是数据终端设备(DTE)和数据通信设备(DCE)之间的接口标准,不同厂家生产的设备,只要它们都具有RS-232-C标准接口,则不需要任何转换电路,就可以互相插接起来。

串行通信程序是MCU与PC机通信的控制程序。发送程序采用查询的方式设计,即把待发送的数据先送到缓冲区中,然后查询串口发送中断标志是不是有空,若有空就发送下一个数据。

接收程序采用中断的方式设计,即当PC机要发数据给MCU时,主动向MCU申请中断,接收中断标志有效,则PC向MCU传送数据。

3 验证方案

3.1 验证平台的建立

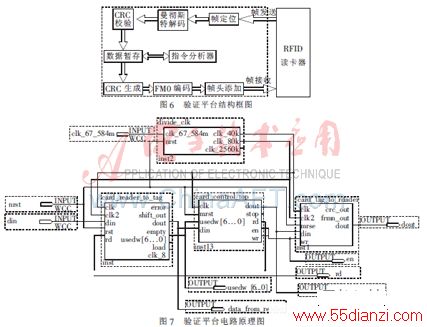

为了验证所设计的读卡器能否完成预期的功能,设计了相应的验证平台[8]。验证平台由数据解码通道、数据编码通道以及指令分析器三部分组成。数据解码通道是对读卡器发送出的数据帧进行解码,提取指令的原始数据;指令分析器是对收到的指令数据进行判断,同时返回相应的数据并发送给数据编码通道;数据编码通道则是对发送来的数据进行编码,再发送给读卡器。

平台采用Verilog HDL硬件语言搭建,选用ALTEra公司Cyclone系列的EP1C6Q240C8芯片为目标器件,使用QUARTus II进行综合验证,其结构框图和电路原理图分别如图6、图7所示。

3.2 测试结果分析

(1)时序分析

通过运行QuartusII 7.1自带的时序分析器,可以得到时序分析的一些参数:tsu(输入建立时间)、tco(时钟到输出延时)、th(保持时间)分别为3.530 ns、13.174 ns、0.751 ns。基频时钟clk最大可以达到89.06 MHz,而ISO/IEC 18000-6 Type B协议规定的基频时钟为40 kHz。从分析本系统的时序结果显示,完全符合协议要求。具体的时序分析结果如图8所示。

(2)功能分析

功能分析以GROUP_SELECT_LT命令为例。 GROUP_SELECT_LT命令是多卡操作中的组选命令,射频卡接到此命令,卡内指定地址的数据与帧中提供的数据进行对比。若卡内数据较小,则返回射频卡的64 bit序列号,否则不作任何响应。GROUP_SELECT_LT命令的命令号为03,地址设为0F,掩码设为FF,64 bit数据全设为F,所以从MCU传给FPGA的命令数据为03_0F_FF_FFFF_FFFF_FFFF_FFFF。原始数据经过FPGA数字信号处理模块处理后,就成了一帧基带数据信号。验证平台将读卡器发来的数据帧进行解码,然后判断指令并返回射频卡的64 bit序列号,经编码后成一帧数据帧发送给读卡器。读卡器收到此帧后即解码,并进行CRC校验,若都没有错,则把解码后的数据传输给MCU。

GROUP_SELECT_LT命令仿真波形图如图9所示,实验证明可实现ISO/IEC 18000-6 Type B协议。

随着RFID相关国际标准的确立(如ISO/IEC 18000)RFID的研发已成为国际性的课题。在诸多RFID工作频段中,UHF频段的RFID技术前景最为看好,也成为现今RFID技术领域研究的热点。

参考文献

[1] 周晓光,王晓华.射频识别(RFID)技术原理与应用实例[M].北京:人民邮电出版社,2006.

[2] 倪荣生.超高频RFID系统的发展和趋势分析[J].中国防伪报道,2007(11):41-47.

[3] 刘韬,楼兴华.FPGA数字电子系统设计与开发实例[M].北京:人民邮电出版社,2006.

[4] ISO/IEC JTC1/SC31/WG4N0722. ISO/IEC FDIS 18000-6:2003(E)[S]. Geneva: ISO copyright offICe, 2003.

[5] 张迎新,雷文,姚静波.C8051F系列SOC单片机原理及应用[M].北京:国防工业出版社,2005.

[6] 范佳林.915MHz RFID阅读器设计[D].大连:大连理工大学,2006.

[7] 陆永宁.非接触IC卡原理与应用[M].北京:电子工业出版社,2006:94-97.

[8] CILETTI M D. Verilog HDL高级数字设计[M].张雅绮,李锵,等译.北京:电子工业出版社,2005.

本文关键字:读卡器 仪器仪表读写器,电子知识资料 - 仪器仪表读写器