ModeslSim仿真需要解决PWM的双向IO端口,PWM的Regs的读写控制时序。

对于双向端口的数据交换,采用读写控制结合三态门可以比较完好的解决。对于大量的Regs读写操作,通过模拟单片机对外围器件的操作。利用Task调用的方式实现。

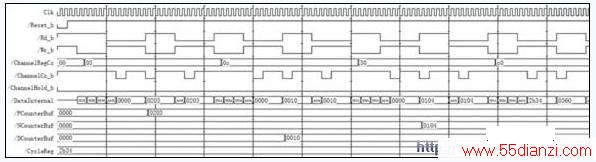

模拟仿真的结果如图4。

图4 读写操作过程

从图4中,可以看到当采用16bits读写时,各寄存器通过内部DataInternal数据总线的传输过程与电路设计要求完全一致。RWLogic与DataInterface模块的功能完全符合设计预想。

图5 输出结果与程序设定的周期和PWM波形完全一致

从图5中,可以看到PWM输出信号,在ClkGen的CycleScale信号的控制下周期输出编程设定的PWM波形,并能异步响应ChannelHold_b信号的输出控制。

PWM的 fPGA 验证,采用8bits数据接口,89c51[4]做外围控制器( 12MHz ),对PWM进行操作。为了方便与单片机接口,将74LS373锁存器内置到PWM中。整个数字设计部分见图6。

图6 PWM+L74LS373电路图(与 51单片机 验证)

通过Synplify Pro编译后的结果显示:

ProjectTopModule : PWMTopFor8051

Estimated Frequency: 72.9 MHz

Total LUTs: 1478 of 4160 (35%)

占用FPGA资源35%。针对51系列的单片机而言,PWM可运行的频率远超过系统频率。因此在读写时序上可以完全保证整个设计的可靠性。

将编译后的pof文件下载到APEX20KE EP20K100E TQ144-2X( ALTEra ) fpga[5]验证板。采用 40MHz 的FPGA时钟。根据先前软件仿真的步骤,将读写操作转换为单片机程序烧录到单片机。最后的结果通过 示波器 我们可以清楚的看到实际输出与设计完全一致。芯片采用.35工艺,一次流片成功后,测试结果显示结果非常理想,实现了当初的设计要求。

本文关键字:暂无联系方式元器件特点及应用,元器件介绍 - 元器件特点及应用

上一篇:42s可编程一次性烧录语音芯片