PRIME - PoweRline Intelligent Metering EvoluTIon 标准是由西班牙Iberdrola电力公司联合有关的 PLC 芯片、系统、电表等厂商,为窄带 PLC 电力线通信制定的远程抄表技术标准,包括物理层和MAC 层的数据传输标准。该技术的协议开放,实施无版权费用,不同厂商的产品能够实现互联互通。TI 采用低成本的 DSP 控制器,以软件的方式来实现 PRIME 协议,相较其他厂商以专用芯片ASIC 的实现方式,提高了应用的灵活性。

事实上,早前TI 已经采用OMAP1808 实现了PRIME 数据集中器的完整功能。本文介绍的方案,主要是将OMAP 平台的DC 方案移植到单芯片Concerto 上,实现一颗芯片完成PRIME 的上层和底层MAC 协议以及物理层协议,适用于低成本的嵌入式数据集中器应用,因此,我们也把该数据集中器方案简称为EDC,即Embedded Data Concentrate。

OMAP1808 平台的 DC 方案基于 Linux 操作系统,而本 EDC 方案基于 TIRTOS 操作系统,上层和下层MAC 通信采用内部数据共享,不但系统精简很多,占用资源少,而且数据更加可靠,除了没有TCP/IP 接口之外,所能管理及连接的节点数量与OMAP 平台的DC 方案无异。

1 EDC 系统架构

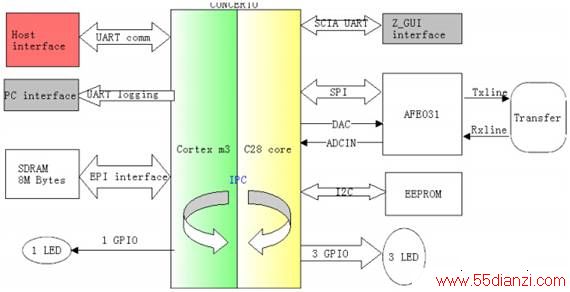

本方案采用 Concerto 系列芯片 F28M35H52C1 作为主芯片,处理 PRIME 协议的 UPPER MAC 及LOW MAC, PHY 层协议。F28M35H52C1 是一款双核的MCU,它内部包含了Cortex m3 主系统和TI C28x 控制子系统两个MCU 系统,每个系统分别有512KB 的Flash 空间,Cortex m3独立使用 32KB RAM,TI C28x 独立使用 36KB RAM,另外还有可配置使用权的 64KB 的共享RAM(在EDC 系统中全部被分配给C28x 使用)和2KB 的IPC Message RAM。在EDC 系统应用中,Cortex m3 核工作主频为 75MHz,它负责处理 Upper MAC 协议, C28x 核工作主频为150MHz,它负责处理 Low MAC 及 PHY 层协议,两个核之间通过 IPC 内部数据共享区机制进行通信。主芯片 MCU 外加一个 8M Bytes 的 SDRAM,由 CM3 核进行访问,用来存储节点信息数据库等数据,目前系统使用的大小约为3M Bytes;另外有一个128KByts 的EEPROM,由C28x访问,用来存储系统掉电参数;模拟前端采用 TI AFE031,支持三相和单相连接,由 C28x 核通过SPI 接口对其进行控制。系统框图如图1 所示。其中,CM3 通过1 个GPIO 口控制一个LED,在系统正常工作时以 1Hz 频率进行显示;C28x 通过 3 个 GPIO 控制另外三个 LED,分别指示C28x 工作状态及PLC 通信状态。

图 1 PRIME EDC 系统架构示意图

2 EDC 方案特性

单芯片实现PLC PRIME DC 完整功能。

提供UART 接口与PC 或用户Host Processor 进行通信,通信速率115200bps,8 位数据位,1 位停止位,无奇偶校验。

提供 PC(Ubuntu Linux OS)客户端软件进行模拟测试,客户端软件通过mgmt及 IEC-432 API 接口与 EDC 上运行的服务器端进行通信,用户可参考这些客户端软件示例代码实现 Host 代码设计,客户端软件包括:

Management tool applicaTIon

Base node conference tool applicaTIon

IEC 61334-4-32 data transfer applicaTIon

硬件设计保留C28x 的SCIA UART 通信接口,便于客户使用TI 提供的PC 端ZCG 工具软件,通过连接PC 的COM 口或USB-UART 转接板至该接口来单独对PLC PHY 层参数进行测试。

3 硬件设计

3.1 参考原理图

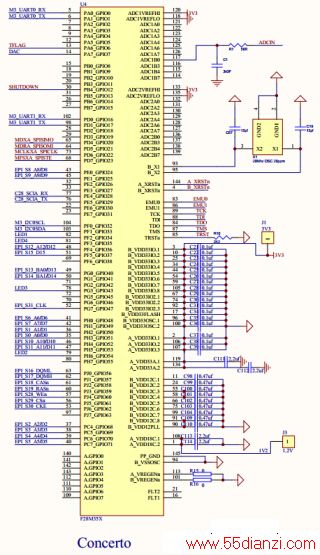

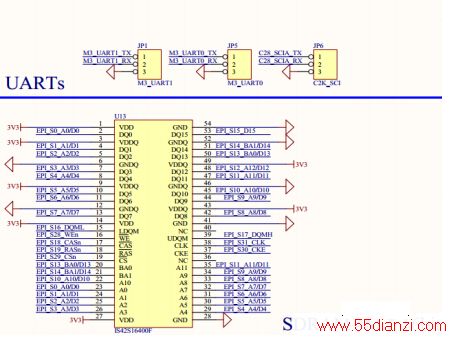

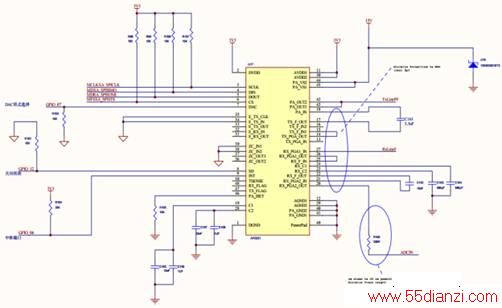

硬件相关的原理图部分设计请参考图2,图3,图4 所示。

图 2 主芯片MCU 参考设计原理图

图 3 SDRAM 及UART 接口参考设计原理图

图 4 AFE031 周边电路参考设计原理图

3.2 电路板

EDC 电路板实物如图5及图6 所示。电路板正面放置MCU, AFE031 及变压器,电源IC 等大部分器件,背面放置了一片SDRAM。MCU 芯片左上方的彩色线连接部分为UART 通信接口及UART 打印信息输出接口,左侧为15V 供电输入接口及电表连接接口,该22 PIN 接口按照中国国家电网《Q/GDW 375.2-2009》标准第 6.3.1 节中对集中器载波模块的接口定义进行设计,其中的 UART 接口连接至 MCU CM3 核的 UART0;右侧黑胶布遮盖部分为外接三相电力线接口,该接口同样按照中国国家电网《Q/GDW 375.2-2009》标准第 6.3.2 节中对集中器载波模块的载波耦合接口定义进行设计,Service node 可以通过该三相电力线接口与EDC 进行单相或者三相的信号连接。EDC 上电正常工作时,图5 所示右下方的LED(LED-4)灯会以1Hz 的频率闪烁。

图 5 EDC 电路板正面图

图 6 EDC 电路板背面图

3.3 EDC与PLC 节点组网连接

本例采用TI 的TMDSPLCKIT-V3 作为PLC 节点,EDC 与两个PLC 节点的连接如图7 所示,EDC 的UART0 接口与Linux PC 客户端通过一个UART-USB 转接小板连接,连接如图8 所示。

图 7 EDC 与PLC 节点连接示意图

图 8 EDC 与PC 连接示意图

4 EDC可以实现的功能

支持多达1200 个节点的注册/注销

支持最多3600 路的Unicast MAC 连接/释放

Keep Alive 功能及自动调节Keep Alive 检查间隔时间

IEC-61334-4-32 逻辑链路层

Appemu数据传输测试

支持节点中继

节点promoTIon 和demoTIon

MulTIcast MAC 连接/释放

单点和多点firmware upgrade

支持使用IEC 61334-4-32 服务的外部应用

支持外部管理GUI

支持Linux 客户端命令进行DC 一致性测试

5 EDC运行需要的目标代码及Linux 客户端软件

Concerto 目标代码:prime_dc_concerto_cm3.out prime_dc_concerto_c28x.out

Linux 客户端软件:uart_intf, mgmt_cli, ext432App, bn_conf_tool

6 PRIME EDC 基本功能演示

PRIME EDC 的功能演示基于一个PRIME 网络进行,该网络由一个base node 和几个service node 组成,EDC 就是其中的base node。功能演示包括以下几个部分:

节点注册、节点注销

Keep Alive 监测

节点连接、断开连接

节点升级(至中继节点),节点降级(至终端节点)

按照IEC-61334-4-32 协议进行数据传输

固件在线更新(单播和群播)

参考图7 的网络连接示意图搭建演示网络,参考图8 连接EDC 的UART1 至Linux PC,给EDC 及service node 加电后,系统将自动完成网络连接。通过在Linux PC 端的进行对应的命令行操作,即可实现以上功能演示。Linux PC 端的命令行操作参考后续章节介绍。

本文关键字:通信 综合通信技术,通信技术 - 综合通信技术