摘要:设计了基于ISO18000-6C标准的USB2.0数据通信协议便携式射频读写器。以ALTEra EP1C3T144为核心控制器、CC1100为RF收发器、CH372为USB接口器件,组成了该硬件系统。经测试,系统收发频率为889 MHz,最高数据传输速率为240 kbps,天线发射功率为1.1 dBm,读写器稳定传输距离为1 m,数据传输准确,系统读写稳定可靠,抗干扰能力强,适用于各种复杂EMI环境。

关键词:ISO18000-6C;高频RFID;EP1C3T144;CC1100;CH372

引言

射频识别(Radio Frequency IdentifICation,RFID)是利用微波进行双向数据传输的一种非接触式射频自动识别技术。RFID系统具有使用寿命长、低功耗、数据传输快速、稳定、安全、可靠,适应性和抗干扰性强等优点,已广泛用于工业控制、消费类电子、医疗电子、现代物流和校园一卡通等方面。RFID技术是现代物联网的核心技术。我国研究RFID技术起步比较晚,受软件和硬件等条件限制RFID技术还未真正实现大规模应用,大多数属于中、低频数据传输,距国外先进技术还有一段距离。本文重点介绍基于Altera公司Cyclone系列FPGA和ISO1800 0-6C标准超高频RFID读写器的软硬件实现方法。

1 系统原理和结构

1.1 RFID系统原理

典型RFID系统由读写器(Reader)、射频标签(RFIDTag)、天线(Antenna)、中间件(Middle Ware)和应用程序(Application Ware)5部分组成。RFID系统结构框图如图1所示。读写器安装在固定位置,通过USB与PC连接,实现数据通信与读写,读写器对射频标签操作实现用户数据更新与存储。由于系统基于ISO18000-6C标准,射频标签要符合该标准,实现用户数据存储;读写器由编解码电路、数据存储电路、射频前端收发电路、天线、电源电路等构成;天线接收和发送超高频微波信号;中间件、中间信息和数据处理软件,对射频读写器和中间件事件过滤、聚合和计算,抽象出对应用软件有逻辑意义的算法;应用程序直接面对用户人机交互界面。由应用软件操作读写器,读写器收发微波信号修改用户射频标签,应用软件是用户体验和判断RFID系统成功的一个重要因素。

1.2 RFID读写器原理

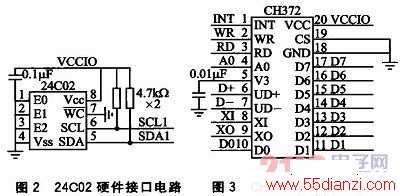

基于FPGA RFID读写器可分为3个模块:FPGA最小系统、USB串行总线接口电路、RF信号收发电路。FPGA最小系统包含FPGA现场可编程逻辑阵列、JTAG配置电路、系统时钟电路、数据存储电路、显示电路、电源电路。RFID读写器控制核心用Altera公司Cyclone系列的EP1C3T144芯片。由于FPGA基于SRAM技术,下载配置芯片用Altera公司配套的EPCS1,下载模式采用JTAG模式,20 MHz有源时钟晶振,0.3寸共阴数码管,外接5 V直流电源,经两级LM1085转换为3.3 V和1.5 V电压,为FPGA内核和引脚供电。数据存储芯片选用Catalyst公司CMOS技术芯片EEPROMCAT24WC02,通过I2C总线与FPGA连接。USB串行总线接口芯片采用南京沁恒公司的USB通用接口芯片。RF信号收发模块选用Chipcon公司的SmartRF03技术和0.18μm CMOS工艺的CC1100芯片作为微波信号收发前端,通过SPI总线与FPGA连接。

在RFID系统中,读写器是连接射频标签和PC机客户端的核心,通过对读写器命令操作,实现用户数据修改、存储等操作。RFID读写器与标签数据传输可以分为从读写器到标签前向链路和标签到读写器后向链路,前向链路与后向链路采用半双工方式通信,数据传输采用ASK调制,前向链路采用PIE码,后向链路采用Miller码,系统采用CRC-16校验码和特殊防冲突算法保证读写正确。RFID通信可分为2步:阅读器首先获得在辐射范围内标签ID号,然后对ID号符合要求的标签进行读写相应操作。读写器与上位机USB数据通信,通过USB设备枚举完成HID人机接口设备识别和数据读写。

2.2 USB串行总线接口电路

CH372简易USB通用串行总线接口集成电路,兼容+5 V和+3.3 V供电,最大工作电流为30 mA,外接12 MHz频率晶振,20引脚SOP封装;兼容USB2.0数据传输协议,支持HID设备热插热拔,内置USB底层通信协议,自动完成标准USB事件枚举;支持数据控制传输、批量传输、终端传输;默认链接端点0所有事件,FPGA负责数据传输与处理,使用方便,CH372硬件接口电路如图3所示。

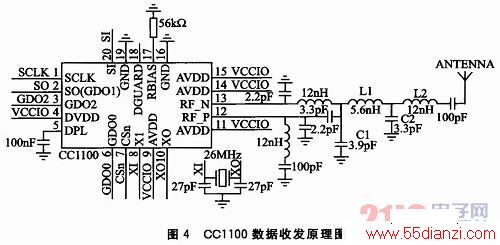

2.3 CC1100 RF收发电路

CC1100是一款极低功耗UHF收发集成电路。其通信效果好、抗干扰性能强、穿透力强、灵敏度高;可自由设置收发频率,可设置范围为300~348 MHz、400~464MHz、800~928 MHz,可编程控制数据传输速率最高可达500 kbps,4线SPI(SI、SO、SCLK、CSn)接口。CC1100正

常工作电压为3.3 V,最高输入电压3.6 V,每个引脚输入电压应相同。868~915 MHz发送模式输出功率为+10 dBm,电流为30 mA,接收最大功率为+10 dBm,硬件自动CRC校验,支持ASK调制解调,调整外围元件可方便调整收发频率。CC1100采用数据缓冲技术,具有2个64字节FIFO,缓冲发送和接收数据。CC1100可软件设置RF发送功率、收发模式、调制格式、信道选择和带宽、数据传输速率、整机工作模式等。

CC1100属于半双工通信,接收和发送在射频控制模块RF CONTRON控制下分时进行,解调由积分器向下积分完成,AGC电路控制回路增益;调制基于直接频率合成,载波信号由晶振与内部PLL电路产生,发送模块和接收模块稍有区别。接收模块包括:低噪声放大器LAN、积分器INTEGRATION、模数转换ADC、解调器DEMODU-LATOR、向前数据误差处理器FEC/INTERLEAVER、包处理PACKET HANDLER、接收数据缓冲器RXFI FO、数字接口电路DIGITAL INTERFACE TO MCU;发送端与接收端不同的模块有:压控振荡器VCO、混频器MIXER、发送数据缓冲器TXFIFO,数据收发由不同模块分时完成。

CC1100具有2种工作状态——空闲状态和工作状态,每种状态对应电流不同。空闲状态可分为等待WAIT状态,内部电流1.9 mA;睡眠SLEEP状态,内部电流400~900 nA;晶振的停振状态仅维持寄存器值不变,内部电流160 nA;工作状态可分为接收(RX)和发送(TX)状态,接收状态根据接收信号强弱内部电流在14.2~15.4 mA范围变化。发送状态下,发送信号功率大小随工作电流变化。14 mA时发射功率为-10 dBm,29 mA时发射功率为+20 dBm。根据工作状态调整工作电流,可实现整机最低功耗。

由于采用ISO18000-6C标准射频空中接口协议,系统采用889 MHz发射和接收频率,改变CC1100第12、13引脚外接电容C1、C2,电感L1、L2的参数可调整射频收发频率,发射天线采用50 Ω偶极子天线。12、13引脚LC网络器件参数可由软件SmartRF studio仿真得到,参考CC1100官方DATASHEET,根据实际情况微调。CC1100数据收发原理图如图4所示。

www.55dianzi.com

3 系统软件设计

3.1 RF收发芯片CC1100软件设计

CC1100操作包括芯片数据读写、寄存器与命令滤波器设置访问、数据包与数据传输速率设置、FIFO访问、低功耗策略等。RFID读写器中CC1100数据传输采用同步连续方式,支持硬件数据包处理、FIFO缓冲、数据白化、交错和前向处理。CC1100数据帧包含前导、同步数据、标签地址、数据长度、读写命令、数据地址、数据、CRC校验码、结束位。其中前导数据、同步数据通过CC1100寄存器设置硬件自动完成、CRC校验码硬件自动完成,其他数据需软件设置或配置寄存器。数据帧结构如表1所列。

本文关键字:读写器 射频技术-RFID,通信技术 - 射频技术-RFID