1 ǰ ��

������,���ƽ�任����Ϊ���������о����ȵ�֮һ,����Ҫ������ѹ���ʵ�Ӧ�ó��ϡ�Ŀǰ,�����ֻ����Ķ��ƽ�任�����˽ṹ[1]���ٶ�������λ��;�ڷɿ������;�ۼ����͡�

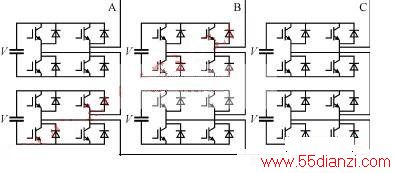

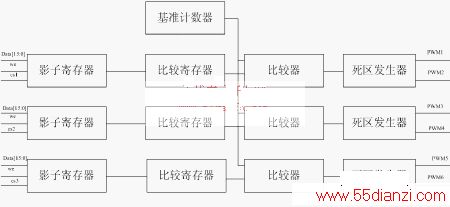

�������˽ṹ��������ȱ��,����Զ���,�����Ͷ��ƽ��Ƶ�����и����ص��ŵ�,���Ľṹ��ͼ1��ʾ����������λ�����ܺ͵���,���ڷ�װ,�����ڵ��ݵ�ѹƽ������,�ɲ�������ؼ������Ա��Ɀ�غ��ܵ��������յ�·�1�����Ҫ���ܻ����ز�������Ʒ����ļ������������ƽ��Ƶ����PWM���巢������ʵ�ַ�����

ͼ1 �������ƽ��Ƶ���ṹͼ

2 �ز�����SPWM����

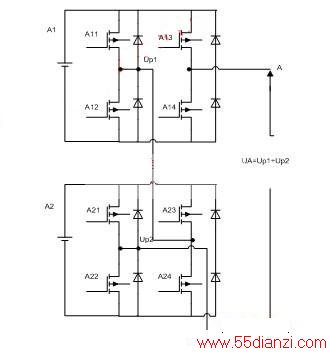

��ν����ʽPWM�������ǽ����Ʋ����ز���Ƶ�ʹ̶�����,���Ʋ�����λҲ���ֺ㶨,��ֻ�����ز�����λ,�Ӷ�����SPWM�źš�����ͬ�ز���λ�µ�SPWM�źŽ����������,�ﵽ����г�������������ʵ�Ŀ�ġ�����֤��,������ ʱ(αΪͬ��ĸ���Ԫ���ز�������Ƕ�,N Ϊ������Ԫ����)[2],���г��Ƶ������ 2N ��,�������˳��������������ƽ��Ƶ��,N=2,����ͬ�༶������Ԫ���ز����90�ȡ���ͼ2��ʾ,����A11��

ͼ2�������ƽ��Ƶ����A��

A14�ز�����180��,A11��A21���ز�����90��,��A21��A24���ز�����180�ȡ�A1��A2������������ѹ��

����

��(1)ʽ��֪UA���ٰ���2F±1�����µ�г��,������2F±1���ϵ�г��������������ΪNʱ,��NF±1���µ�г��������ȥ��

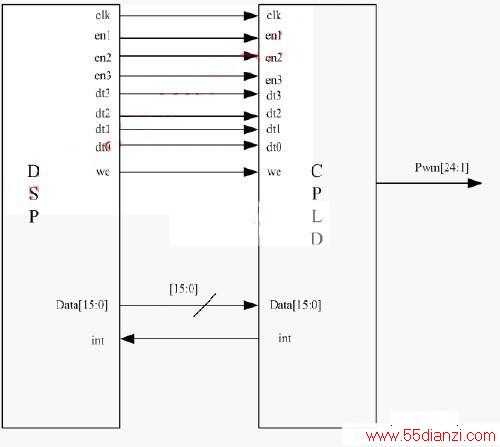

3 ����CPLD���������ƽ��Ƶ��PWM���巢������ԭ��

һ��DSPֻ�ܲ���12·PWM����,���������ƽ��Ƶ����24·PWM����,����˫DSP���24·ʱ����ͬʱ�Ե�����,����ø��ӿɱ��������CPLD��ʵ�֡���ǰ,���ӿɱ��������CPLD���ִ����ֵ�·������ѳ�Ϊ���ɻ�ȱ������,CPLD�ڲ��������������Ӽ���������,���п��������õļ��ٸ��Ĵ�����I/O��,���ҿ������ڶ̿��������ʵ�ֶ��ֹ��ܶ�����Ķ�Ӳ����·��

��ͼ3ΪDSP��CPLD���ɵ�PWM���巢�����Ŀ��ƿ�ͼ��

ͼ3 DSP��CPLD�Ŀ��ƿ�ͼ

CPLD����DSP��ʱ��CLK,��ʵ��ʱ��һ��,dt0,dt1,dt2,dt3ΪDSP���ĸ���ַ��,����ѡͨCPLD��ʮ��·PWM���巢������һ·,intΪ�ж��ź�,ÿ���ķ�֮һ���ز�����Tc��һ��,weΪDSP��д�ź�,ֻ�е�we��csn(n=1��12)ͬʱΪ�͵�ƽʱData����д��Ӱ�ӼĴ���,����csnΪ�ĸ���ַ�����������,��ͼ4��ʾ��

����

ͼ4 PWM������ԭ��ͼ

��Ȼ,ͬһ��İ˸����ع�ֻ����·�ز�,����������ͬһλ�õĿ��ع����ز���ͬ,�ʿɹ���һ�����������������ͼ4����PWM��������ԭ����ͼ4�еĻ�������Ϊһ�Ӽ�������,�������ֵΪһ���ز�����TC,���ȽϼĴ�����Ϊ����ֵ,����������������ֵ��ȽϼĴ������ʱ,�Ƚ������������ƽ��ת,ÿ������������������ʱ,����һ��ʹ���źŰ�Ӱ�ӼĴ����е�����ֵ����ȽϼĴ������ɱȽ��������ԭʼPWM������������������������űۻ�������·PWM����

4 VerilogHDL��������

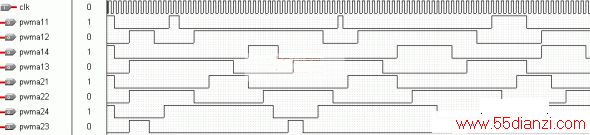

����ͼ4��ԭ��ͼ,Ӧ��VerilogHDLӲ���������Խ�����ơ�����ѡ��ALTEra��˾��EPF10K30Aϵ�е�CPLD,ͨ��MAX+PLUS����������,ͼ5��ʾΪA��8·PWM�����źš����ͱ���,ͬһ�ű�������·�ź����������㻥����ϵ,����һ��������ʱ��,ʵ��“�ȶϺ�ͨ”,��ͬ�ű�֮�����λ��ȷ��

����

ͼ5 A��PWM���沨��ͼ

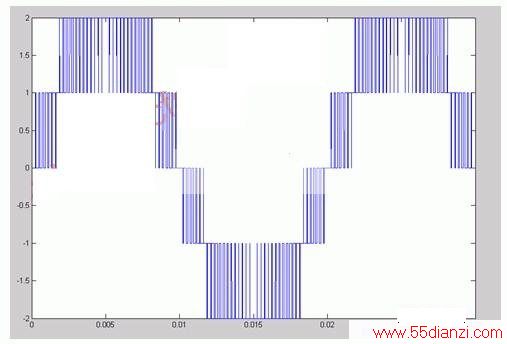

ͼ6Ϊ��������ԭ��,����MATLAB/SIMULINK��������ѹ���ƽ����,���е��Ʊ�Ϊ0.9,�ز���Ϊ32��

���Ĺؼ��֣����巢���� Ƕ��ʽϵͳ-��������Ƭ��-�����豸 - Ƕ��ʽϵͳ-����

��һƪ������Ƕ��ʽ���漼������ϵ�ṹ�о�