为了建立SystemC和SystemVerilog的高效集成解决方案,让诸如信号和事务处理这样的基层概念在语言设计中,尽管已经在各自的语言中 进行了各自方面的优化,在语义上又能够跨越语言分界实现有效的映射。实际上,SystemC和SystemVerilog的标准化组织,OSCI和 ACCellera,已经认识到在这两种语言之间建立有效接口连接机制的需求。

SystemC和SystemVerilog集成的核心支持了混合层级结合的建模,而有能力创建部分处于事务处理级和部分处于具体硬 件级的仿真模型。因此,集成让SystemC和SystemVerilog能够在不同的抽象层级上进行通讯。

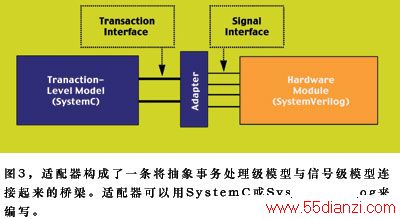

一个典型的应用实例是将一个SystemVerilog RTL模块集成到整个系统的一个SystemC模型中,例如,为了实现早期集成检查。由于SystemC典型情况下应用在事务处理级,就有必要使用一个作为抽象层级之间桥梁的适配器(图3)。

这些适配器的目的在于将事务处理转换成信号操作,而反之亦然。这样,就可以让设计的一部分在事务处理层次上进行仿真,而另一些部分在具体硬件层级上进行仿真。采用这种方法,设计人员拥有对于仿真具体层级的完全控制。

这些适配器可以用SystemC或以SystemVerilog(图3)来编写。使用一项SystemC适配器是相当直接的方式,并且以将 SystemC信号映射到SystemVerilog信号为基础,反之亦然。而以SystemVerilog来缩写转换器时,典型情况下能够提供更高的性 能,但要求在SystemC与SystemVerilog之间建立事务处理级接口。

SystemC与SystemVerilog之间的事务处理级接口

在SystemC中,将通讯与功能区隔开来的目的导致了接口概念的形成。在SystemVerilog中,与接口类似的概念也进行了设计。虽然 SystemVerilog接口和SystemC接口并不完全一致,它们在语言上具有足够的匹配度,能够提供这两种语言之间的有效事务处理级连接。 SystemVerilog接口是一种能够将信号捆绑在一起的结构,并且具有与SystemC接口完全一样的接口方法。通过使用 SystemVerilog基于DPI的服务层,验证引擎可以直接将SystemC接口映射在SystemVerilog接口上,从而可以从 SystemVerilog验证平台中直接调用SystemC事务处理级模型。

例1所示为在参考文献[3]中所述的以SystemC编写的simple_bus的模块接口部分。它描述了接口方法burst_read。而 simple_bus的整个代码可以在任何SystemC 2.x版本的安装版本中找到。但是,simple_bus是如何实现此接口方法的,例如,使用了什么样的总线带宽或使用了哪一类型的仲裁,对于该接口方法 的调用者来说都是不可见的,因此,可以在体系结构开发中很方便地进行改变。

例2所示为simple-bus的一个SystemVerilog接口部分,这个总线可以直接映射到如例1所示的SystemC接口。为了确保 SystemVerilog接口向SystemC成员的正确映射,其实现通过一个SystemVerilog的直接过程接口(DPI)服务层来完成。

这样就可以实现如例3所示的从SystemVerilog验证平台中直接调用SystemC对象的接口方法。

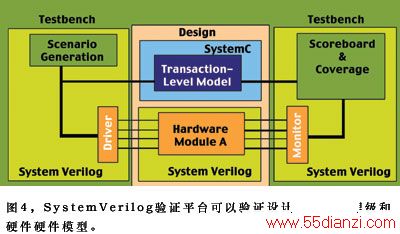

有了这种能力,验证团队就可以充分利用SystemVerilog的验证平台技术来验证SystemC事务处理级模型,并可以使用SystemC事务 处理级模型作为硬件验证流程的参考模型,这点在图4中进行了概略的描述。此外,SystemVerilog功能覆盖和断言可以用于实现完整的由覆盖率驱动 的事务处理级模型的验证解决方案,为SystemC模型提供新型和前所未有的验证能力。

Synopsys的Discovery验证平台是这类集成验证环境最好的实例之一,它同时集成了对SystemC和SystemVerilog的支 持。它提供了高性能的RTL验证,包括仿真和形式分析、体系架构开发以及提供一个对广泛的测试平台所需的基础支持,来处理事务处理级建模的验证。

通过观察目前的SoC设计,我们可以大致了解为什么ESL工具和方法在控制设计成本和帮助准时发布产品方面起到了关键性的作用,并且了解到那些影响到SoC性能和成本的关键性决策是在项目早期通过采用事务处理级建模方法建立的虚拟原型做出的。

SystemC是一种非常适合于创建、仿真和分析设计的事务处理级模型的语言。SystemVerilog是理想的硬件实现语言。SystemC和 SystemVerilog的良好结合能支持混合(事务处理和硬件)模型。此外,这项结合让SystemVerilog的强大验证能力能够在事务处理级模 型的验证工作中充分发挥,而相同的验证平台还可以适用于硬件验证工作。

SystemC和SystemVerilog结合起来提供了当今先进芯片所需的一套从ESL至RTL设计流程的真正的、基于标准的解决方案。通过将 SystemC和SystemVerilog结合到一个单一的验证环境中,可以高效地建立和验证分析体系结构所需要的事务处理级虚拟原型,并在设计工作的 早期开发内嵌的软件。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术

上一篇:基于CPLD的双口模块设计方法