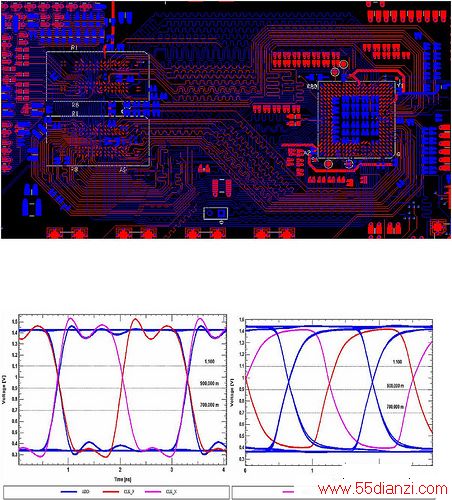

图9: 只有在TOP和BOTTOM层走线的DDR3的仿真波形

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络,其时钟频率在800 MHz,数据通信率为1600Mbps)

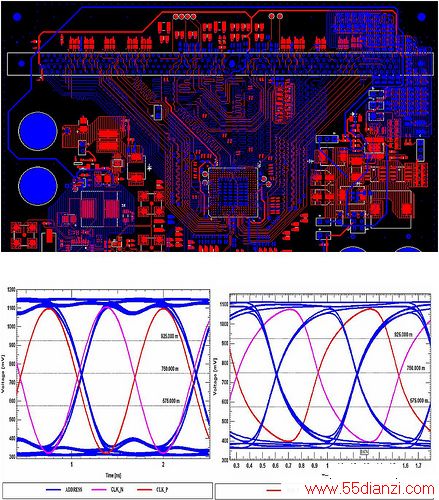

图10: 只有在TOP和BOTTOM层走线的DDR2的仿真波形

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络,其时钟频率在400 MHz,数据通信率为800Mbps)

图11: 只有在TOP和BOTTOM层走线的DDR3-DIMM的仿真波形

(左边的是ADDRESS和CLOCK网络,右边的是DATA和DQS网络)

最好,图12显示了两个经过比较过的数据信号眼图,一个是仿真的结果,而另一个是实际测量的。在上面的所有案例里,波形的完整性的完美程度都是令人兴奋的。

图12: 800 Mbps DDR2的数据信号仿真眼图(红) 和 实测眼图 (蓝)

11. 结论

本文,针对DDR2/DDR3的设计,SI和PI的各种相关因素都做了全面的介绍。对于在4层板里设计800 Mbps的DDR2和DDR3是可行的,但是对于DDR3-1600 Mbps是具有很大的挑战性。

本文关键字:线路板 EDA/PLD技术,单片机-工控设备 - EDA/PLD技术