为了满足工业控制系统多功能和数据处理能力的需求,设计了基于CPCI总线的一体化数据处理中心。系统以FPGA芯片为硬件控制核心,利用硬件描述语言Verilog进行编程,采用自顶向下和模块化的设计方法,实现了在同一嵌入式产品上集成光纤通信、A/D、D/A、CPCI总线、SDRAM存储等功能,实现了系统的一体化、小型化。实际应用表明本系统稳定可靠、易于维护,满足工业控制领域的需求。

近年来,随着工业控制技术的发展,在工业控制领域中,对控制系统的功能、灵活性和数据处理能力提出了更高的需求,本文从实际工程应用出发,研究并实现了一种基于CPCI总线的一体化可配置数据处理系统。

本设计利用可配置的现场可编程门阵列(FPGA)与具有高可靠性、高密度性的CPCI总线相结合的方法,将众多数据处理功能集成在同一个嵌入式系统板卡上,实现了系统的一体化、小型化。

1 系统总体结构

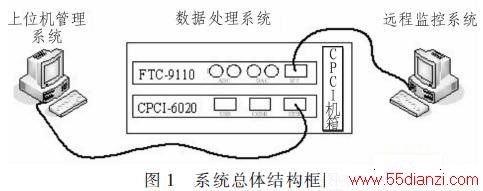

本系统主要由上位机管理子系统、远程监控子系统和数据处理子系统组成,总体结构如图1所示。

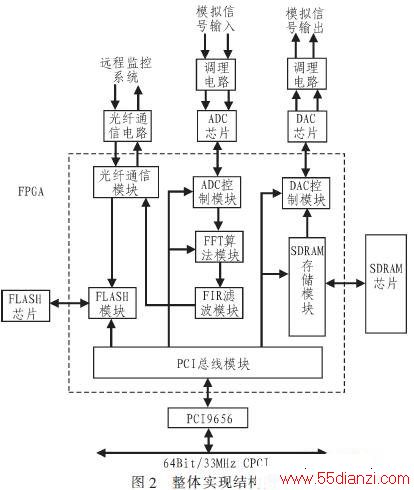

上位机管理系统主要用于显示系统工作状态并提供人机交互界面。远程监控系统通过光纤连接到距离系统1 km以外的位置,实现系统的远程监控。数据处理子系统包括CPCI-6020单板计算机和FTC-9110数据处理单板两部分,CPCI-6020单板计算机用于解释上位机发送的命令并对数据处理中心进行控制。FTC-9110数据处理单板是数据处理的核心部分,也是文中介绍的重点,其整体实现结构如图2所示。

FTC-9110数据处理中心以FPGA为硬件处理核心,通过内部构建的ADC控制模块、DAC控制模块、FLASH模块、SDRAM存储模块、光纤通信模块、PCI总线模块实现对外围设计的A/D数据采集电路、D/A数据输出电路、FLASH存储电路、SDRAM数据存储电路、光纤通信电路以及CPCI总线接口电路的控制,通过与单板计算机的灵活配合,实现对数据的实时处理、高速传输。

2 数据处理流程

系统的数据处理主要以FTC-9110为中心,利用单板计算机对FPGA内部构建的各个模块的灵活控制,实现数据的处理,其数据处理流程如下:

1)利用ADC芯片前端设计的信号调理电路,将输入的单端模拟信号转换为差分信号送入芯片的差分输入端。

2)ADC芯片对输入的信号进行采样,并将采样所得数字信号传送至FFT算法模块。

3)利用FFT算法模块对采集数据进行频域分析,分析数据的结果传送至FIR滤波模块作为滤波输入信号,滤波后输出数据传送至光纤通信模块。

4)光纤通信模块通过高速并串转换模块对滤波输出数据进行8B/10B编码,将16位的数据转换为20位的串行数据,输出速率最高可达1.5 Gbps,然后该高速串行数据进入光电转换模块,传送至远程监控系统。

5)单板计算机控制PCI9656工作在DMA传输模式,通过PCI总线模块和SDRAM存储模块将DAC输入数据写入SDRAM芯片。

6)读取SDRAM芯片数据传送至DAC控制模块,DAC芯片对输入数据进行数模转换,并通过后端设计的调理电路,使信号最终以电压形式输出。

3 硬件设计

硬件设计将重点介绍DAC电路及控制模块、PCI接口控制模块、光纤通信电路及控制模块的设计。

3.1 DAC电路及控制模块设计

DAC电路由D/A转换电路和信号调理电路两部分组成。D/A转换电路采用了ADI公司的电流输出型芯片AD9717,在芯片输出后端设计的调理电路,将电流输出转换为电压信号输出。

FPGA通过SPI接口对DAC内部寄存器进行配置,控制其工作方式。为了方便对内部寄存器配置,FPGA内部设计了相应的寄存器,上位机可以通过对相应的寄存器设置进而改变内部寄存器的值。

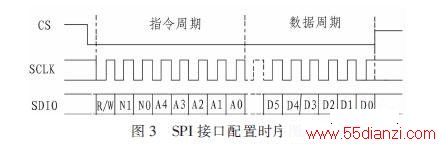

SPI接口由串行时钟(SCLK)、串行数据输入/输出(SDIO)、芯片选择(CSB)3个配置引脚组成,配置时序如图3所示。

SPI接口配置时序由指令周期和数据周期两部分组成,发送的前8个数据(R/W、N1NO、A4-A0)为指令周期,R/W为数据读写控制位,N1NO为数据字节个数控制位,A4-A0为数据地址控制位。指令周期发送结束后是数据周期,数据方向由R/W决定,数据量由N1NO决定.写数据在SCLK上升沿有效,读数据在SCLK下降沿有效。本模块设计的关键代码如下:

3.2 PCI接口控制模块设计

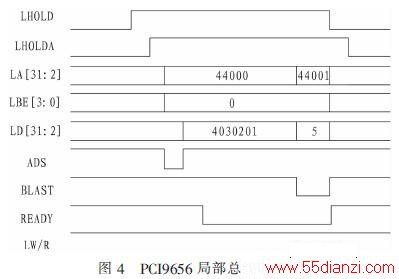

PCI桥芯片主要用于解释单板计算机发送的指令,实现相互间数据通信。本系统采用PLX公司的PCI9656芯片,工作在C模式下,局部总线时序如图4所示。

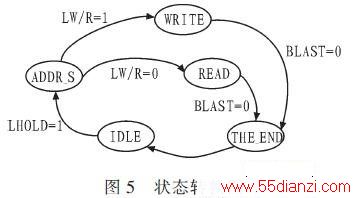

其中LHOLD、BLAST、LA[31:2]、ADS、LW/R等信号由PCI9656驱动,LHOLDA、LBE[3:0]、READY信号由FPGA驱动。通过模块内部设计的状态机实现对局部总线的控制,具体实现过程如图5所示。

1)IDLE状态 系统上电或复位后,处于IDLE状态。在IDLE状态时,FPGA监测LHOLD信号,当单板计算机访问FPGA时,LHOLD信号变为高电平。FPGA监测到该高电平后,立即使LHOLDA信号为高电平,转入ADDR_S状态。

2)ADDR_S状态 在此状态下,FPGA监测ADS信号,当ADS信号变为低电平,地址信号LA[31:2]有效,同时对输入的读写信号进行判断,若为读操作,转入READ状态,若为写操作,转入WRITE状态。

3)WRITE状态 FPGA控制READY信号为低电平,以使总线上的数据有效,FPGA可以控制LBE[3:0]信号,以对传输的数据字节进行选取。并监测BLAST信号,当监测到BLAST信号为低电平时,表示传输最后一个数据,转入THE_END状态。

4)READ状态 同WRITE状态相似。

5)THE_END状态 数据传输结束,FPGA监测BLAST信号变为高电平同时将READY信号变为高电平。当LHOLD信号变为低电平后,LHOLDA信号变为低电平,转入IDLE状态,等待下一次传输。

3.3 光纤通信电路和控制模块设计

本设计中的光纤通信电路由并串转换电路和光传输电路组成。并串转换电路采用了TI公司的TLK1501芯片,通过内部的8B/10B编码,将16位并行数据分成2个8位数据进行编码,编码后的数据为20位,再通过并串转换发送出去;光传输电路采用FINISAR公司推出的FTLF1321SIM TL光模块,将串行数据进行光电转换输出。

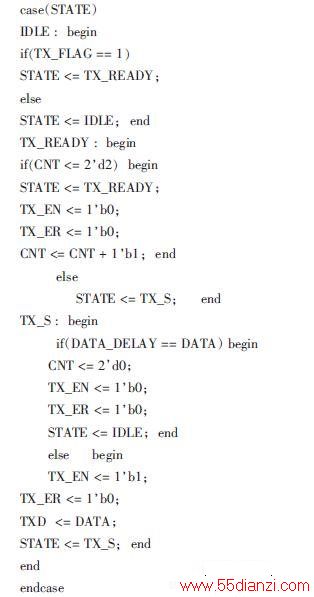

光纤通信模块内部有一个状态机,上电或复位后,处于IDLE状态。模块对传送标志信号(TX_FLAG)监测,如果有传送标志(TX_FLAG=1),转入TX_READY状态。在正常传送数据前,需要对芯片进行同步操作,模块控制信号TX-EN、TX-ER为00,连续发送3个空闲码,使TLK1501进入

同步模式,状态机转入TX_S状态。在TX_S状态下,如果发送有效数据,模块控制TX_EN、TX-ER为10,进行数据的正常发送,发送数据结束后,转入IDLE状态,等待下一次传输。在接收数据时,模块监测RX-DV,RX-ER信号,如果RX-DV,RX-ER为10,正常接收数据。模块设计的关键代码如下:

4 结论

本文通过对多种功能接口电路进行研究分析,最终实现了在同一块嵌入式板卡上集成光纤通信、A/D、D/A、CPCI总线、SDRAM存储、FLASH存储等功能。系统以FPGA芯片为处理核心,利用模块化的思想进行设计,使系统方便扩展、易于维护和升级。经过长期的工程实践验证,本系统运行可靠稳定,能够实现在复杂工业控制系统中对数据灵活控制、实时处理和高效传输。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术