图中还有一个高频处的平坦区,这是源于VCO的输出缓冲。这个区域对周期抖动很重要,而一般对长期抖动则相反,如下式所示:LdB(F)≈10×log10[(1/PSIG)×(FOSC)2/ (Q×F)2]。从式中看到,对某个振荡器频率,当功率增加1倍时,相位噪声降低3dB。增加功率是改善相位噪声性能的一种有效方式,但可能很昂贵。在所有其它方面不变的情况下,改善20dB的相位噪声要付出100倍功率的代价。另外一种改善相位噪声的方式是增加谐振回路的品质因数。品质因数增加一倍,相位噪声减半,即改善6dB。采用CMOS工艺时, 电感 结构经常限制了可以实现的品质因数。通常品质因数是在7-15的范围内,随很多因素而改变,包括频率和金属层厚度等。LC型VCO的调谐范围与品质因数之间也存在着一种折衷,更高的品质要付出较小调谐范围的成本。如采用深亚微米CMOS工艺,相同功率的典型环型振荡器和LC型振荡器的相位噪声大约相差20 dB。这种差异表明谐振回路结构对相位噪声的优点。

如前所述,σ1的值很难在时域中测量。然而,在频域中这种测量就相对简单了。用σ12=F2×L(F)/FOSC3可以计算出VCO的周期抖动σ1,式中F是偏移频率,L(F)是F处的相位噪声,而FOSC是振荡频率(参考文献4)。在此例中,在2GHz振荡频率、 1MHz 偏移的-100dBc/Hz环型VCO的周期抖动是112fs rms。而2GHz振荡频率、1MHz偏移的-125 dBc/Hz LC振荡器得到的σ1值为6.3fs rms。这些值通常都太小,不能在时域中直接测量,缓冲噪声和示波器噪声都足以淹没它们。

从PLL带宽可以计算出长期抖动,以及相应的σ1值,公式是σCO=1/(4πFL/FVCO)1/2。同样,这个计算假设是一个过阻尼PLL,只有VCO噪声,没有电源噪声。如带宽为100 kHz,则σ1为112 fs的环型PLL长期抖动约为4.5 ps rms,而σ1为6.3 fs的LC PLL的长期抖动为270 fs rms。如果将带宽增加到1MHz,则两个长期抖动值都将减小√10,分别为1.4fs和85fs。这种计算可以对更高的带宽持续下去,但很多因素限制了带宽,而抖动则不会持续减小。

限制带宽的主要原因之一是PLL的稳定性。对于恰当的相位裕度,带宽一般只有基准率的1/20。对高性能的PLL,低的环路带宽可减轻基准时钟的穿通。抑制基准时钟的尖刺通常需要一个不超过基准率1/100的带宽。其它限制PLL带宽的理由包括对delta-sigma调制与基准噪声、环路滤波器,以及电荷泵噪声的抑制。

PLL面积

与性能与功耗一样,面积也是PLL的一个重要规格。PLL的性能水平基本上决定了它的面积。选择一种LC型VCO(而不是环型VCO),可以得到性能的大幅增长。对于一只电感的设计,一般基于LC的VCO尺寸至少有300μm×300μm,甚至更大些。而另一方面,环型振荡器尺寸可以是40μm×40μm或更小。一般情况下,LC振荡器的调谐范围要窄于环型振荡器。因此,有时必须在同一个PLL中使用多种VCO,去实现宽的调谐范围,这就进一步增加了面积。

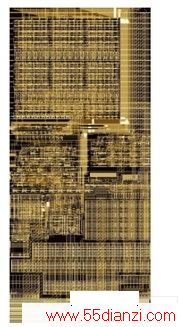

PLL中另外一个面积随性能而显着增加的部件是环路滤波器。一个集成的环路滤波器可以占位达500μm×500μm或更多。随着PLL性能的下降,可以减小电阻、电容以及电荷泵的电流,用噪声的代价来减小面积。用0.13μm CMOS可以做出一个SONET/多协议时钟IC(图5)。图中清楚地显示了四核LC VCO。PLL的面积大约为1.4mm2。长期抖动小于500fs rms,带宽为50 kHz。PLL的功耗约为70mW,取决于工作模式。

图5 这个PLL片芯使用一只LC振荡器,提供了出色的抖动规格

用0.13μm CMOS可以做一个环型小数N PLL(图6)。PLL的面积为0.09mm2,这要比图5中LC PLL的十分之一还小。长期抖动在1 MHz带宽时低至3ps rms,根据工作模式,功耗约为5mW。这个面积大部分是数字的。数字块包括一个delta-sigma调制器、一个预 分频器 、一个后分频器、反馈分频器,以及 控制电路 。模拟面积要比LC PLL模拟面积的十分之一还小。

图5和图6中两个PLL说明了为什么没有万能的SoC PLL解决方案。第一种PLL的抖动几乎能适应所有SoC应用。但是,其面积和功耗要比第二种高出10倍。而第二种PLL的长期抖动又要高6倍,相同带宽下则要高20倍。

图6 这个PLL片芯使用了一只环型振荡器,面积与功耗都只有LC振荡器的十分之一,

付出的代价是较差的抖动性能

PLL SoC各种折衷因素中最重要的是长期抖动。如果长期抖动规格放松,则可以采用小型、低功耗的环型PLL。较严格的长期抖动规格就需要使用大量的硅片面积和功耗,用LC PLL满足要求。然而,对于很多在两种极端之间的应用,选择并不明确,必须做仔细的分析,实现PLL功耗和面积的最优化。

本文关键字:暂无联系方式EDA/PLD技术,单片机-工控设备 - EDA/PLD技术