Cr = [CD*27] *(R – Y)+ COFFSET ([ ]符号表示取整运算)

各参数的取值见表1[2]。

表1 各参数值

CA0.299 CC0.492

CB 0.114CD0.877

YOFFSET 16 COFFSET 128

3.3 图像压缩控制

ZR36060的控制接口示意图如图3所示,VCLK和VCLK2是需要外部提供的时钟信号,由FPGA产生的PIXCLK为25MHZ,满足系统要求。 VCLK是VCLK2的分频,并要求与VCLK2同步。

本系统选择ZR36060工作状态为:8位代码从模式,视频同步从模式,8位视频总线宽度。ZR36060的接口可分为视频接口、主机接口和代码接口三部分。视频信号由视频接口Y[7:0]输入,主机接口通过DATA[7:0]对芯片内部寄存器设置,控制工作状态,压缩后的码流通过代码接口 CODE[7:0]输出到存储器中缓存。8位代码从模式下,主控制器的数据总线DATA[7:0]通过读写HostData对ZR36060的内部寄存器进行设置和读取,代码总线CODE[7:0]从CODEFIFO读写JPEG数据。行同步信号HSYNC接到图像传感器的LVAL引脚,场同步信号 VSYN接到传感器的FVAL引脚。奇偶场指示信号由FPGA给出,每采集到FVAL的上升沿,IND信号翻转一次,以指示奇偶场。

3.4 以太网数据传输

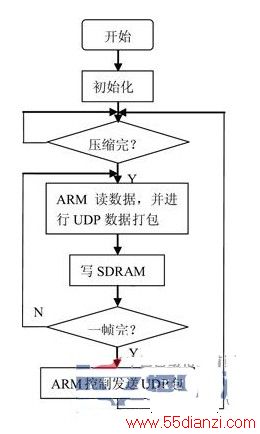

本系统采用UDP/IP协议来实现图像数据的网络传输。压缩后的图像数据经ARM进行UDP数据打包后,存储在SDRAM中。一个完整的数据帧格式包括以太网头、IP头、UDP头和一行图像数据,其系统工作流程图见图4所示。ZR36060 每压缩完成一帧,就由S3C2410读取并写到SDRAM中,然后判断是否读完一帧图像数据,读完后则发送UDP包,将图像数据通过以太网发送到网络。

图 4

4 小结

本文提出了一种基于FPGA和ARM的视频采集处理系统,其特点在于设备接口和视频信号处理的全数字化,系统结构紧凑,体积小巧、响应快速;基于FPGA的前端处理更增加了图像处理算法升级的灵活性,适用于工业远程监控等多种场合。后期还可在采集端加入相应的图像处理算法,以提高图像质量。

参考文献:

[1] 陈晓敏, 王学进, 王志华, 张利. JPEG 编解码芯片ZR36060在远程视频监视系统中的应用[J]. 电子技术应用, 2006. 10.

[2] 魏博, 肖文, 王丛琳, 戎路. 基于FPGA 的CMOS 图像传感器的驱动开发[J]. 光学与光电技术, 2008, 10: 56-58.

[3] Gabor Szedo. Color-Space Converter: RGB to YCrCb. Xilinx Corp, 2006.

[4] 吴继华, 王诚. Altera FPGA/CPLD设计[M]. 人民邮电出版社, 2005.

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术