2.4 显示模块设计

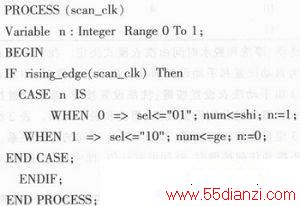

本模块用于在7段数码管上显示当前状态剩余时间,其输入为控制模块输出的当前状态剩余时间和扫描时钟。首先,将输入的剩余时间由秒转换为分钟(四舍五入);然后进行分位,分为个位ge和十位shi(显然剩余时间不超过100分钟,最多2位);最后通过动态扫描在2个共阴极的七段数码上交替显示个位数字和十位数字。当交替频率高于28 Hz时,由于人眼的视觉残留效果,这2位数字看上去是同时显示在2个七段数码管上。动态扫描进程的VHDL代码如下:

3 结束语

我们在QUARTusⅡ软件开发平台上,基于模块化的设计思想,使用VHDL语言完成洗衣机控制器设计、编译和仿真,并下载到FPGA硬件实验箱上进行测试。仿真波形和测试结果表明该洗衣机能正确实现各种设计功能,该设计方案切实可行。

上一篇:基于FPGA的数字电子钟设计