2 工程实现

实际项目中,对中频数字处理单元的主要指标要求为:

(1)中频频率500 kHz;

(2)调制类型:USB,LSB,AM,CW;

(3)接收机灵敏度≤60 μV(Signal—to—Noise—and—Distortion Ratio,SINAD≥12 dB);

(4)AGCGC特性收中频500 kHz输入3.5(-36.1 dBm)~350 mV(3.9 dBm)时,DSP音频输出变化≤2 dB(10 kΩ)。

(5)音频输入≥100 mV(600 Ω)时,500 kHz中频输出≥-31 dBm。

(6)发射机互调特性:500 kHz中频输出≤-37 dBm(50 Ω),双音互调≤-45 dB。

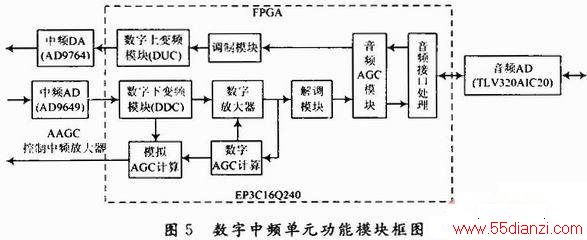

2.1 数字中频单元硬件平台

针对设计要求,中频A/D器件选用AD公司的AD9649-20芯片,其最高采样率20 MS/s,支持差分输入,14位输出,1.8 V供电功耗仅有45 mW。中频D/A器件选用AD公司的AD9764芯片,它的采样率为125 MS/s,14位输入,差分输出,3 V供电时功耗45 mW,休眠功耗小于25 mW,具有28脚SOIC和TSSOP两种封装形式。采用FPGA作为核心处理器,选用ALTERA公司的EP3C16Q240器件。硬件平台框图如下所示。

2.2 工作流程

接收时:中频输入的500 kHz模拟中频信号经AD9649-20采样后(采样速率4.608 MHz),数字信号并行输出至FPGA;数字下变频模块把中频信号下变频为基带信号,对应的采样率从4.608 Mb/s变为9.6 Kb/s(总抽取率为480)。基带信号先经AGC模块处理,此模块的2个输出AA GC和DAGC分别用来控制前端模拟中频放大器和后端的数字增益。之后数字基带信号进入调制解调模块得到用户所需信息,再通过音频DAC输出至话筒。

发送时:输入音频信号经过音频A/D变换后进入FPGA音频处理模块,通过音频AGC处理后在调制解调模块进行调制(用户可以指定USB. LSB,AM,CW四种调制类型),调制后数据采样率为9.6 kHz,FPGA的上变频模块经过480倍的内插,最终输出数据速率为4.608 MHz、中频为500 kHz的中频信号通过中频DA器件AD9764输出到射频单元,混频到射频并进行功率放大滤波后发射。

3 系统测试

3.1 测试方法

3.1.1 DDC测试方法

信号源输出频率为501 kHz.幅度为100μV,12.3μV的正弦波到本系统的中频信号输入端,本系统的音频信号输出端接至综测仪进行测试。测试结果如图6所示。

3.1.2 DUC测试方法

信号源输出频率为1 kHz,幅度为100μV的正弦波到本系统的音频信号输入端,本系统的中频信号输出端接至频谱仪进行测试。测试结果如图7所示。

上述实现方案用于实际电台中,通过大量的室内测试和室外远距离测试,通话效果良好,实测性能指标达到国内领先水平。并且由于采用了纯数字的中频处理技术,使电台的成本控制、可靠性、可维护性、整机的体积和功耗,以及功能的可扩充性都得到极大的改善。

3.2 测试结果分析

图6(a)在100μV信号输入幅度下,音频在600 Ω,输出2.45 V的情况下音频失真度<1%;图6(b)在满足SINAD=12 dB的时候,中频信号输入幅度为12.3 μV即可,完全满足接收系统要求(系统要求中频信号输入幅度为50μV要满足SINAD=12 dB)。

由图7(a)可见,在近端(10 kHz)满足信噪比大于等于50 dB。近端无杂散;由图7(b)可见,在远端(200 kHz)杂散抑制大于等于70 dB。

5 结语

本文设计了一种短波民用电台的中频数字处理单元及基于FPGA的实现方法,同时也对音频信号的处理流程做出分析研究。由于FPGA在设计和修改上的灵活性,使其比ASIC更加适合实现数字上下变频及多模式调制解调功能。本文方案测试结果性能良好,已在实际软件无线电电台中得到应用,具有推广应用价值。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:FPGA开发的基本流程及注意事项