内容摘要:利用FPGA实现了信号的采集与频谱分析系统,对系统进行了模块划分,并分别给出了各模块的设计要点,完成了模拟信号采集模块、快速傅里叶变换模块、存储模块以及VGA显示模块的设计。最后对设计的各模块进行了功能与时序仿真,验证了系统设计的正确性与可靠性。试验表明,该设计可以实现信号的采集、频谱分析与显示等功能,系统稳定可靠。

关键词:A/D转换;信号采集;频谱分析;快速傅里叶变换;FPGA

数字信号处理技术飞速发展,其信号来源往往是模拟信号的A/DC输出。该频谱分析系统主要实现的功能包括对模拟信号进行采集,并对采集到的数字信号进行快速傅里叶变换(FFT),最后将频谱分析结果显示在VGA上。系统的核心部分采用ALTEra公司的FPGA芯片CycloneII实现,采用ADI公司的AD7655来实现待分析模拟信号的A/D转换。

1 系统组成

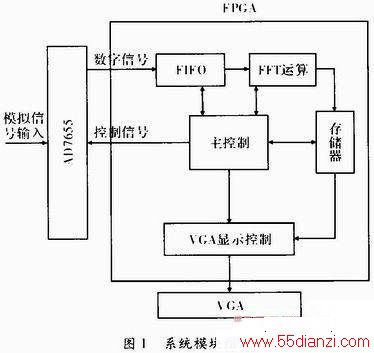

系统通过FPGA控制AD7655芯片采集待分析的模拟信号,并对A/D采集所得来的数字信号进行FFT变换,计算结束后将结果放在存储器中,FPGA以存储器中的数据作为数据源进行控制,VGA将信号的频谱分析结果以图形的方式显示。系统由A/D采集模块、主控制模块、FIFO模块、FFT运算模块、数据存储模块、VGA控制模块等6个模块组成。各模块之间的关系如图1所示。

2 系统设计

2.1 A/D采集模块

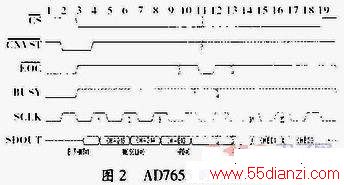

系统控制模块在接收到采集使能信号后,便会启动A/DC来采集原始模拟信号。设计采用16位低功耗A/D转换器AD7655对模拟信号进行采样。AD7655有4个通道,1 Mbit·s-1采样率,输入模拟信号的范围为0~5 V。该芯片的时序如图2所示。

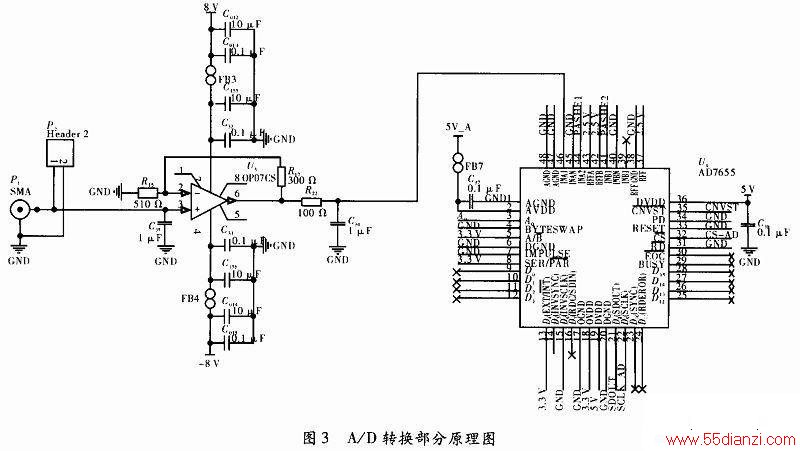

输入待测模拟信号经过调理电路之后满足AD7655模拟输入电平的要求,AD7655采用模拟5 V,数字5 V与接口3.3 V供电,由FPGA的主控制模块控制AD7655进行A/D转换。模数转换部分如图3所示。

2.2 FIFO模块

FIFO是一种先进先出的数据缓存器,他与普通存储器的区别在于没有外部读写地址线,使用简便,缺点是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样,由地址线决定读取或写入某个指定的地址,FIFO一般用于不同时钟域之间的数据传输。

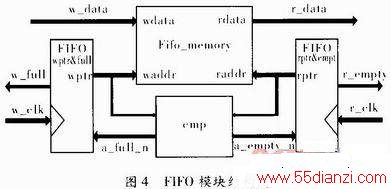

FPGA将经过A/D转换后的16位数据存储到FPGA内部的FIFO存储器中,之所以选择FIFO而没有选择双端口,RAM作为缓冲器是因为FIFO不需要地址信号。当FIFO的状态为“满”时会向FPGA内部的主控制模块发出请求,主控制模块允许之后将数据写入FFT运算模块用于存储实部的双口RAM中作为FFT运算的初始数据。FIFO的数据宽度与A/DC的输出数据宽度一致,其深度是进行FFT运算的点数。系统中每次采样1 000点进行频域分析,为避免产生时域混叠现象需满足频域采样点数N≥1 000,设计取频域采样点数N=1 024。所以FIFO缓冲器的宽度为16位,深度为1 024,结构如图4所示。

2.3 FFT运算模块

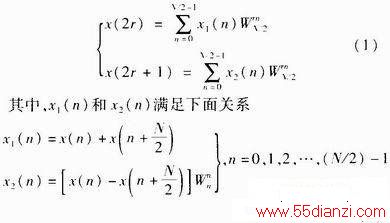

离散傅里叶变换(DFT)开辟了频域离散化的道路,使得数字信号处理可以在频域采用数字运算方法进行。快速傅里叶变换(FFT)是DFT的快速算法,FFT运算模块是本系统的核心模块。在基2快速算法中,频域抽取法FFT是一种常用的快速算法,即DIF—FFT。其数学模型为

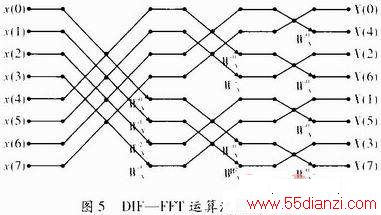

系统采用按频率抽选的顺序输入,倒序输出结构,这种结构中的每一级运算都是固定的,便于寻址,适合于在FPGA上实现,其运算流图结构如图5所示。

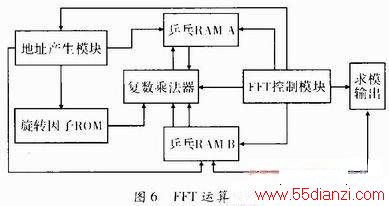

FFT运算模块主要由乒乓RAM、蝶形运算单元、存储单元、地址产生单元、控制单元等组成。FFT运算模块的设计采用了乒乓操作,系统有两块乒乓RAM,每一块由两块完全相同的双口RAM组成。在具体计算过程中,A乒乓RAM中的一块参加运算,另一块从外部接收下一次FFT运算的数据。B乒乓RAM中也有一块参加运算,另一块向外部输出上一次运算的结果。一次FFT运算完成后,两块乒乓RAM做一次乒乓,如此反复,直到FFT运算结束并将结果求模输出到结果存储器。采用乒乓操作主要是为了保证运算模块不会为了数据的载入而停止运算可以有效提高运算速度。

蝶形运算单元是整个FFT处理单元的重要部分,直接影响整个FFT单元性能。一个基2蝶形运算要进行1次复乘、2次复加。为提高运算速度采用并行运算,采用4个实数乘法器、3个实数加法器和3个实数减法器组成。数据格式选择定点16位二进制补码。设计时必须考虑乘法器速度,将会直接影响整个FFT处理单元的运算速度,乘法器的两输入均为16位,输出32位。因为乘法器中带有旋转因子项,所以乘法运算后不应改变输入的幅值即乘法器的输出仍为16位,因此要对输出数据进行截取,截取其中16位作为加法器的输入。一个蝶形运算在一个时钟周期内即可完成。FFT运算模块结构如图6所示。

存储单元包括2块乒乓RAM、一块RAM和一块ROM,蝶形运算的输入数据和输出数据分别存储在两个双口乒乓RAM中,RAM用来存储FFT的模,旋转因子事先计算好并存储在ROM中。数据存入结果存储器前,要将倒序输出变为正序输出。转换方法是将地址的最高位和最低位交换,次高位与次低位交换,依次类推。

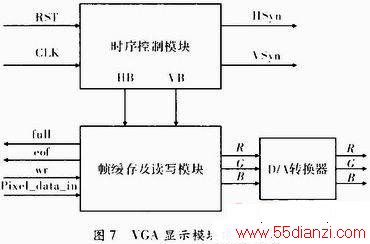

2.4 VGA显示模块

VGA显示模块的设计,完成的功能:(1)在一定的工作频率下,产生正确的时序关系,即工作时钟信号、水平同步信号(HSyn)、垂直同步信号(VSyn)、消隐信号之间的关系。(2)在正确的时序控制下读出帧缓存中的像素数据,同时在当前帧显示完毕时,向视频存储控制器发信号,使视频存储控制器能够及时刷新帧缓存中的像素数据,图7是VGA显示模块视图。

其中CLK是VGA显示模块的时钟信号,RST是复位信号,FULL是VGA显示模块中帧缓存满标志信号,当帧缓存中数据满时,VGA显示模块将此信号发送给视频存储控制器,WR为VGA显示模块中的帧缓存写操作信号,Pixel_data_in为读入到VGA显示模块的帧缓存中的像素数据,该数据来自视频存储器,而EOF则表明VGA显示模块的帧缓存已空,可以重新读入一帧新的像素数据以供显示。信号HSyn是由VGA显示模块产生的水平同步信号,发往显示器的VGA接口,信号VSyn是由VGA显示模块产生的垂直同步信号,发往显示器的VGA接口。信号尺是经D/A转换器分离的像素数据中的红色基色信号,发往显示器的VGA接口,信号G是经D/A转换器分离的像素数据中的绿色基色信号,发往显示器的VGA接口,信号B

是经D/A转换器分离的像素数据中的蓝色基色信号,发往显示器的VGA接口。

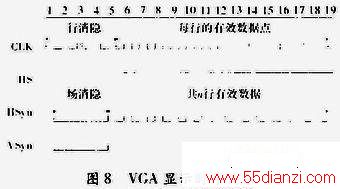

其中VGA显示时序驱动是完成设计的关键。在VGA显示控制过程中,完成一帧扫描所需要的时间成为垂直扫描时间,其倒数称为垂直扫描频率,又称刷新频率。图8是VGA显示的时序关系。

3 仿真结果

该系统选择ALTEra公司Cyclone II系列的EP2C70F89618芯片来实现,FFT模块是设计的核心部分。系统时钟100 MHz,实验输入模拟信号为余弦信号,初始化参数设置FFT的点数为1 024点,旋转因子精度为16 b,复数乘法器结构为“4 Mults/2 Adders”。经综合时序分析得知:其工作时钟频率68.82 MHz。编译成功后的RTL级电路描述如图9所示。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术