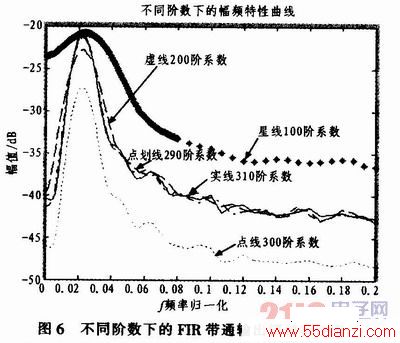

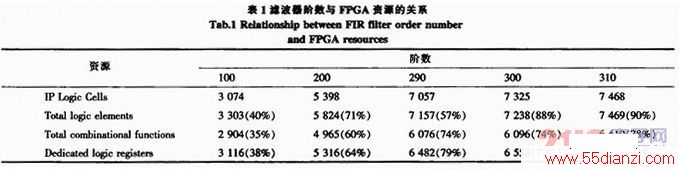

阶数越高,其通频带越小,衰减特性也越尖锐,越接近我们需要设计的FIR带通滤波器,但不足之处就是耗费资源,其资源利用情况如表1所示。

2.2 不均匀采样数据对FIR数字滤波器的性能影响

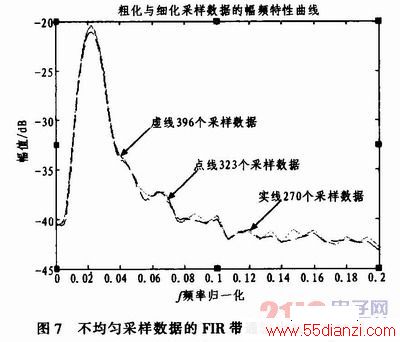

不均匀采样,就是在幅度衰减剧烈的频率附近多选取数据采样点,而在其它幅度变化不剧烈的频段少选取采样点。在保持FIR滤波器阶数不变的前提下,改变每组采样数据的采样点个数,每组采样数据均采用不均匀采样,可以得到不同的频率向量f与幅度向量a,利用函数fir2()就可以得到不同的FIR滤波器特性系数。再将系数导入IP核,对产生的FIR带通滤波器的实际输出进行采样,再将采样的幅值和频率值导入MATLAB,得出的幅频特性曲线如图7所示。

知道采样数据的多少对FPGA的资源利用率无多大影响,但是会影响FIR带通输出波形的抖动,采样数据越密集,越能得出我们需要的幅频特性图。

3 结论

以上实验表明,在FPGA上用FIR IP Core实现FIR数字滤波器是一种很简洁有效的方法。如果FPGA资源比较大时,我们尽量选取高阶的FIR滤波器,这样能实现较好的滤波器性能;如果FPGA资源有限时,我们只能尽可能的选稍微高阶的滤波器,但是可以通过细化采样数据来达到较好的性能。

本文关键字:滤波器 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术