时,会出现随着码元数的增加,cos()*cos()的值越来越小,最后计算出的

误差较大。为避免这种情况,应减少复数相乘的次数。

具体的做法是:

(1)根据QDPSK的星座图对待调制的码字进行编码:00→3,01→1,10→5,11→7。

(2)将前后码字所对应编码后的码进行模8加,即得到当前码字所对应的相位信息码。相位信息码只有8种可能{0,1,2,…,7},对应的△θ分别是{0,π/4,π/2,…,7π/4},这样查表即可得到△θ。

(3)计算

,这样只需计算一次复数乘就可以得到做IFFT所需的信息。

(4)记录本码字所对应的相位信息码,以用于下一个码字的相位信息码的计算。

3.4 前向纠错(FEC)编码

所有未知输入数据应具有附加的冗余位,用以纠正由传输媒介引起的错误。校验位由一个缩短的Reed—Solmon码(15,11)来计算,其生成多项式为

其中,a是伽罗瓦域的一个非零元素,GF(24)为GF(2)模

形成的多项式域。所采用的是缩短为(7,3)的RS编码。

RS(7,3)编码采用3位16进制码生成4位16进制的校验监督位,即12 bit信息编码生成16 bit校验监督位,也就是RS(28,12,16)编码。为了减小DSP的开销,采用的编码思想是预先建立校验表而后逐位判决逐位编码的方式。具体步骤如下:

(1)建立校验表。编写信息位是0800H,0400H,0200H,…,0008H,0004H,0002H,0001H所对应的校验位分别是:03959H,08DBDH,04FCFH,02E6EH,…,0156FH,0983EH,0DC87H。这样可以建立校验表:

.int 03959H,08DBDH,04FCFH,02E6EH

.int 037EEH,08A77H,045AAH,02855H

.int 02ACDH,0156FH,0983EH,0DC87H

(2)根据校验表逐位编码。假设需要编码的信息是A81H共3位16进制信息,将其转换二进制数为101010000001B。第1位是1,则取A1=02C7 AH,第2位是0,则取A2=0,第3位是1,则取A3=0935BH,第4位是0,则取A4=0,…以此类推得到A1,A2,…,A12,将这12个校验码进行异或得到这3位信息的4位校验码。

3.5 交织

交织是一种差错控制技术。它的目的是使误码离散化,将突发差错信道变为离散差错信道,再通过纠正随机差错来改善数据传输质量。原理把信息码流在时间顺序上按一定规则打乱,即相互穿插交织后再发送到信道中去。若交织后的码流出现突发差错,再经过解交织还原成原来的码流顺序,则将突发连片差错分散成随机差错,更加容易进行纠错。由于接收机在收到了整个交织块并进行解交织后才能解码,所以交织带来一个固有延时。

选取每种速率3种交织度来实现。分别是无交织(交织度为1)、短交织(交织度为4)、长交织(交织度为36)。

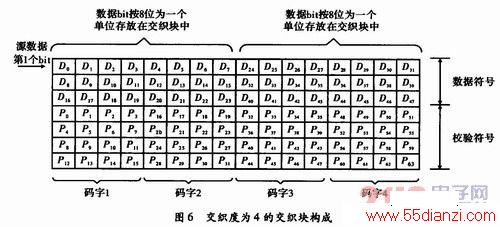

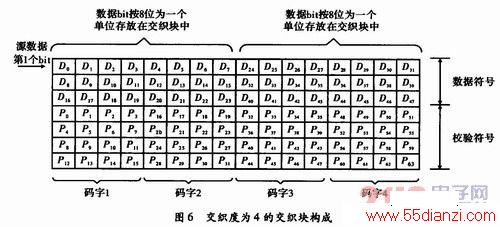

这里所说的交织度(1、4、36)指的是交织块中一行所包含的4 bit码字数。以短交织为例,说明一个交织块的构成。

源数据以8 bit作为1个单元,按列向交织区填充,如图6所示。RS编码时取4 bit×3行数据作为1个码字进行编码,形成4 bit×4行的校验位。图6中对信息位(D0,D1,D2,D3,D8,D9,D10,D11,D16,D17,D18,D19)进行RS(7,3)编码后生成校验位为(P0,P1,P2,P3,P4,P5,P6,P7,P8,P9,P10,P11,P12,P13,P14,P15),并且依照图中的格式存放在交织块的对应位置。当一个交织块填充满后,就可以按行进行一个交织块数据bit的输出,(D0,D1,D2,D3,D4,D5,…,P47,P60,P61,P62,P63)。

3.6 分集方式

分集技术是通过多个信道接收到承载相同信息的多个副本,由于多个信道的传输特性不同,信号多个副本的衰落就不会相同。接收机使用多个副本包含的信息能比较正确的恢复出原发送信号。本系统采用的是包含时间和频率分集的方法。

www.55dianzi.com

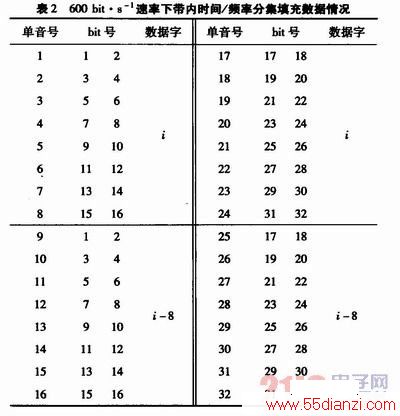

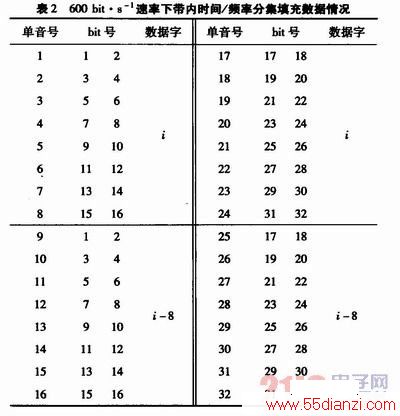

在不同的数据速率下,1个码元所用到的数据字大小不同,可以将300~1 200 bit·s-1各种速率情况总结如下:1 200 bit·s-1速率时不做分集,一个数据字需要64 bit信息;600 bit·s-1速率时,一个数据字需要32 bit信息;300 bit·s-1对应的是16 bit的数据字。换句话说,就是在300 bit·s-1数据速率下,只要有16 bit新信息,就可以进行一个码元的调制。数据速率为600 bit·s-1的情况,如表2所示。

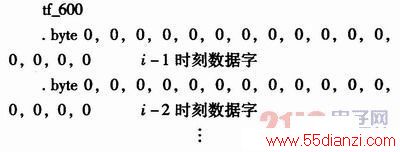

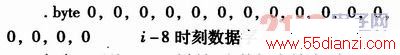

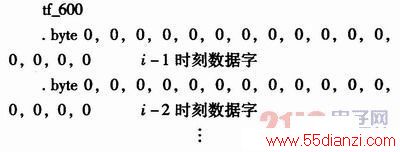

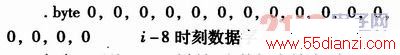

在600 bit·s-1数据速率情况下,要求在1~8及17~24号数据音传送当前数据字,9~16及25~32号数据音传送的是之前第8个码元传送的数据字。在DSP内存中开辟一个空间存储过去8个码元用到的数据字。

每次只要从i-8时刻提取数据字填充到9~16及25~32号数据音,而后进行32音调制即可实现带内时间频率分集。

4 结束语

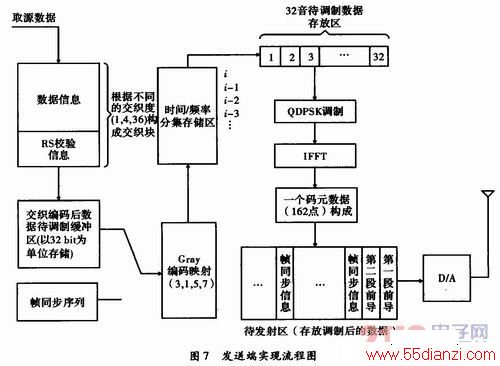

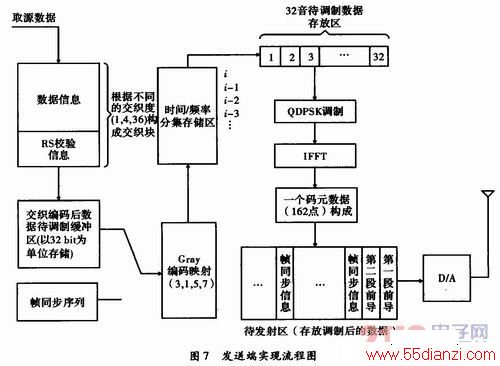

发送端在DSP中实现的具体流程,如图7所示。

具体实现时遇到的问题和难点:

(1)交织度、RS编码方式、带内时间/频率分集方式都随数据的不同而不同,所以要考虑到相对应程序的通用性,设定入口参数和参数下载的过程,这样减小程序代码段的开销,但是增加了编程的复杂度。

(2)从源数据区向交织区填充数据时,要注意剩余bit的保存。从交织区向待调制区填数据时,要注意剩余bit的保存。

(3)在超级块和超级块的衔接处,存在剩余bit调制发送的问题。要把当前超级块所剩下的bit全部调制发送完,才能进行下一个超级块的构成和发送。

上一页 [1] [2]

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术