对部队中已大量装备使用的跳扩频电台的维护与测试需要性能稳定的跳扩频信号源,因此非常必要研制使用方便、性能可靠的跳扩频信号源,以解决部队急需,从而提高部队的机务维修保障能力。随着电子技术的发展,尤其是近十年来数字化技术、超大规模集成电路和软件方面的新技术新成果不断涌现,使得设计高可靠、高精度、高稳定可携带方便的测试系统成为可能。与传统测试系统中的跳扩频信号源相比,本跳扩频信号发送系统采用了FPGA、DDS等多种先进技术,具有体积小、重量轻、成本低、集成度高、精度高、可靠性强等优点,能够有效地模拟产生需要的跳扩频信号,为机载跳扩频电台的测试提供可靠的激励信号。

1 系统设计总体方案

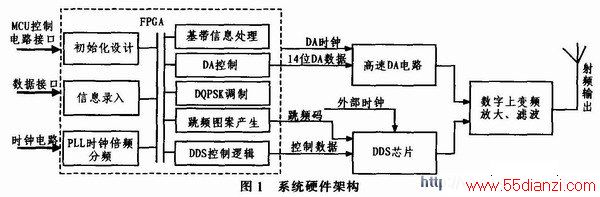

针对信号源需求分析,设计系统总体方案如图1所示。FPGA接收主控单元(MCU)传递的信息数据,接收数据源速率为4.8 kb/s。基带处理部分进行差错编码,编码处理后的基带信息数据以9.6 kb/s信息速率输入成帧电路,组帧后信息速率为38.4kb/s。中频处理电路接收38.4 kb/s信息速率的数据,并进行扩频和DQPSK调制。扩频调制PN码码片速率为1.228 8 M码片/秒,即每个调制符号对应64个码片。系统中频输出8.192 MHz DQPSK数字数据。系统带宽跨度为UHF(超短波)105~156 MHz,分了16个跳频点带宽≥45.5MHz。跳频最小间隔≥2.5 MHz,跳频速度1 000 Hop/s。

2 关键模块研究与实现

2.1 DQPSK调制

中频调制使用数字化DQPSK(相对相移键控)调制,该调制技术能有效利用数据带宽,同时采用差分编码解决QPSK调制时出现的相位模糊问题,保证了数据的正确解调。DQPSK调制框图如图2所示。

差错控制编码采用(217)卷积编码,码率为1/2。交织采用块交织,交织器长度为384,即一大帧的长度。为保证数据的连续发送,交织采用两个交织器轮流工作。交织后数据以9.6 kb/s交给DQPSK调制,经差分串并转换,以64位码长的M序列对转换后码率减半的数据进行扩频调制和成形滤波。数控振荡器(NCO)产生正交调制的波形,对成形滤波后的信号进行正交调制。

2.1.1 滤波成形

DOPSK调制后的信号存在以下问题:调制后的信号将出现瞬时变化,这将不可避免地导致信号的瞬时频谱的扩散,如果无失真地传输该信号就要求有很宽的信道带宽,这在信号传输中是无法实现,唯一有效的途径就是采用滤波技术限制频谱,这就需要基带滤波。基带滤波是在时域上扩展符号,如果设计的不好,在接收端将会引起严重的码间干扰(ISI)。无码间扰准则可表示为:

![]()

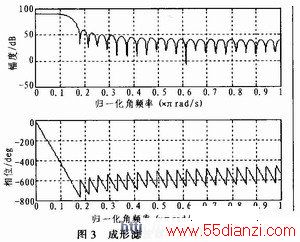

平方根升余弦滚降滤波器有一个平滑的过渡带,通过引入滚降系数来改变传输信号的成形波形,可以减少抽样定时脉冲误差所带来的影响。本设计中采用56阶,滚降系数为0.35的平方根升余弦滤波器,每个符号抽样8个点。系统中所设计的成形滤波器频域响应如图3所示。

www.55dianzi.com

2.1.2 NCO模块设计

数控振荡器NCO可以在高时钟频率下通过相位累加来实现,相当于一个给定频率发生器产生一个理想的正弦或余弦波样本。NCO的输出频率可表示为:

![]()

其中,Bθ(n)表示查找表地址的位数,△0表示采样周期相位增量,fclk是系统时钟。

该NCO的设计是在FPGA中采用查表法来实现,它主要由地址累加器和储存正弦值的ROM表组成。系统时钟clk输入按关键字的步长累加相位地址,读出对应ROM中的幅度值。查找表的存储调用了ALTERA公司提供的波形数据存储器LPM_ROM文件来实现。LPM_ROM是在QUARTus II8.0中

使用Mega Winzard Plug-In Manager来创建定制的。在创建的同时对其参数进行初始化设置,使Quartus II8.O编译器自动地在EP2C8Q208C8芯片中的EAB中实现ROM函数的合适部分。设计使用了22个逻辑单元,小于1%,节省了硬件资源。

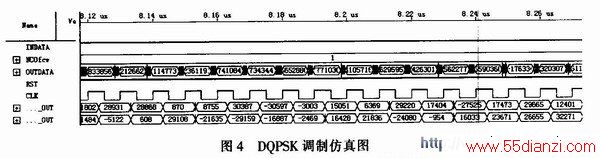

2.1.3 DQPSK的顶层设计及仿真

DQPSK顶层模块主要由3部分组成:差分串并转换、成形滤波和正交调制。DQPSK调制仿真结果如图4所示。

2.2 DA电路设计

HI5741是Harris公司生产的电流型14位D/A转换器,+5 V和-5.2 V操作,最高转换速率可达100 MHz,输出信号为TTL/CMOS电平。转换器提供20.48 mA的满量程输出电流并且包含一个输出数据寄存器和带隙电压参考。低灵敏度干扰能量和优良的频域性能。由于HI5741采用了分离结构可以消除由于输入数据不对称引起毛刺的脉冲。硬件连接电路如图5所示。

2.3 跳频部分设计

2.3.1 DDS跳频码

DDS输出频率一般表达式![]() ,式中k为频率码关键字,fc为时钟频率,而k由下式确定:

,式中k为频率码关键字,fc为时钟频率,而k由下式确定:

![]()

式中,A31,A30,…,A1,A0,对应于32位码值(0或1)。当A0=1,其他为0时,则输出频率最低,即分辨率:![]() 。当A31=1,而A30,…,A1,A0,均为0时输出频率最高:

。当A31=1,而A30,…,A1,A0,均为0时输出频率最高:![]() 。在实际工程中,受到低通滤波器的限制,一般输出的频率foutmax≈40%fc。这时一周期只有两个取样点,根据Nyquist定理已达到抽样定理的最小允许值,A31=1,以下码值只能取0。

。在实际工程中,受到低通滤波器的限制,一般输出的频率foutmax≈40%fc。这时一周期只有两个取样点,根据Nyquist定理已达到抽样定理的最小允许值,A31=1,以下码值只能取0。

在108~155.975 MHz的带宽内,频率最小间隔大于2.5MHz,将规定的带宽分为16个跳频点,由于在实际应用中,还有一些点的杂散信号很大,而且离主频很近,无法去除。所以应该避免输出这些频点。这些频点为靠近fc/3、fc/4、fc/5、fc/6……的频点。跳频点数为16,并基于频率转换公式![]()

![]() 计算所对应的32位码值。

计算所对应的32位码值。

www.55dianzi.com

2.3.2 跳频图案设计

跳频图案采用对偶宽间隔跳频序列,基于m序列,利用非连续抽头(L-G)模型,构造宽间隔跳频伪随机序列,自相关性能、互相关性能较高接近最佳跳频序列族,提高信号的抗干扰性。设计中基于L-G模型的非连续抽头模型,采用本原多项式![]()

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术