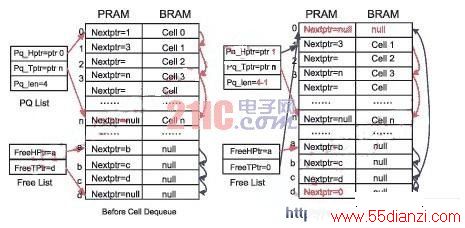

图7 读出操作的Free Lis链表结构

Read Control模块由PQ List的首地址0读出相应的BRAM中的内容,同时读出PRAM中对应的下一跳地址1,更新地址1为新的首地址。

Free List相对于堆栈模式增加尾指针d。Free List在回收地址时维持首指针a不变,将尾指针d更新为刚释放的地址0,同时地址d中写入下一跳指针0。这样一次BRAM的读出操作同样需要一次PRAM的读取操作及一次PRAM的写入操作。对于链表方式的空闲地址队列Free List,在每个读、写周期必须进行两次PRAM的写入操作及两次PRAM的读取操作,PRAM的效率不高。

针对两种空闲地址队列的效率及对DRAM的影响,在很多系统中采用了折中的方法,即在PRAM中使用链表方法管理空闲地址队列Free List,在片内采用堆栈模式另建一个空闲地址队列Free List,在这种情况下,每个读、写周期需要三次PRAM的操作。

在实际系统中,BRAM的带宽与PRAM的带宽一般为TM的瓶颈,PRAM主要受限于访问的次数,而BRAM受限于接口带宽。

在10G的TM系统中,片内数据总线的位宽定为128位,系统时钟定为150MHz,BCELL的大小定为64B。在这种情况下,读取操作和写入操作均为4个时钟周期。在满足10G系统的需求下,读取、写入操作周期为7个时钟周期。在前面曾计算过,在满足10G TM系统的情况下,BRAM采用64位 DDR II SDRAM,接口时钟使用250MHz即可满足数据接口的需求。PRAM采用32位ZBT SRAM ,接口时钟使用系统时钟,每个PCELL为64位,每个读、写周期需要6个时钟周期完成。在实际系统中采用ALTEra FPGA,BM的设计可以满足10G的TM线速工作的需求。

在40G核心网的TM系统中,片内数据总线的位宽为256位,系统时钟采用250MHz(在40GE的系统中可选用200MHz)。采用DDR II SDRAM,接口时钟使用333MHz,则192位的BRAM可以满足40G的TM需求。此时,BCELL可为96B、192B、384B,在这里选用1

92B。当BCELL选用192B时,读取操作和写入操作同样均为6个时钟周期。在满足40G系统的需求下,读取、写入操作周期为9个时钟周期。PRAM采用48位QDR SRAM,接口时钟使用150MHz,每个PCELL为96位,在每个读、写时钟周期内,PRAM最多可被操作5次。在采用Altera FPGA的情况下,BRAM采用192位 DDR II SDRAM,PRAM采用48位QDR SRAM,BM的设计可以满足40G的TM线速工作的需求。

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术