数字 电压表 是大学物理教学和实验中的重要仪表,其数字化是指将连续的模拟电压量转换成不连续、离散的数字量并加以显示。传统的实验用模拟电压表功能单一、精度低、体积大,且存在读数时的视差,长时间连续使用易引起视觉疲劳,使用中存在诸多不便。而目前数字万用表的内部核心多是模/数转换器,其精度很大程度上限制了整个表的准确度,可靠性较差。本文采用National SEMIconductor。公司性能优越的8位A/D转换器 ADC0809 对模拟电压采样,以一片高性能 FPGA 芯片为控制核心,以软件实现了诸多硬件功能,对电压信号的转换结果进行准确实时的运算处理并送出显示。系统的主要功能都集成在一块芯片上,大大减少了系统的分立元件数量,降低了功耗,增加了可靠性,较好地实现了电压的精准测量。

1 设计方案比较

采用双积分式模/数转换器为核心器件,称为双积分式电压表。在一个测量周期内,将被测电压Ui加到积分器的输入端,在确定的时间内进行积分。然后切断输入电压,在积分器的输入端加与Ui极性相反的电压U,进行定值积分,但积分方向相反,直到积分输出达到起始电平为止,从而将Ui转换成时间间隔量进行测量。只要用计数器累计时间间隔内的脉冲数,即为Ui之值。电路简单,便于维护。但电压表的测量精度完全受限于模/数转换的精度。而且系统无升级空间。

另外,采用单片机作为系统的控制核心。输入信号经模/数转换后送到单片机进行数据处理,根据不同电压信号计算出不同数值,并送出显示。这种方案优点是的单片机技术成熟、运算功能较强、编程灵活、设计成本也较低,能较准确地测量输入电压。但在单片机系统中必须使用许多分立元件组成其外围电路,整个系统显得十分复杂,可靠性较低,抗干扰能力差,而且功耗高。

采用现场可编程门阵列即FPGA为系统核心,是当今电子产品设计的热门发展方向。系统最大限度地将所有器件集成在FPGA芯片上,体积大大减小、集成度高,可靠性高。而且逻辑单元控制灵活、适用范围极广,实现了大规模和超大规模电路的集成。其硬件功能完全由软件编程实现,修改调试方便,在不改变原有电路的基础上便可实现系统升级。较好地克服了另外两种方案的缺陷,具有自己独特的优势。综合上述分析,采用FPGA技术,优势明显。

2 系统工作原理

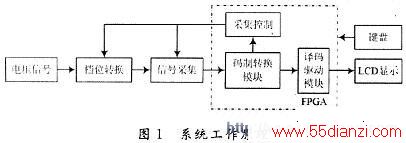

首先,被测电压信号进入A/D转换器,FPGA中控制信号模块发出控制信号,启动A/D转换器进行转换,其采样得到的数字信号数据在相应的码制转换模块中转换为显示代码。最后译码驱动模块发出显示控制与驱动信号,驱动外部的LCD模块显示相应的数据。通过外部的键盘,可以手动对系统进行复位控制和档位选择,不同的档位决定不同的电压输入范围,在程序中实现自动转换。基本工作原理框图如图1所示。

3 关键电路设计

3.1 A/D转换电路

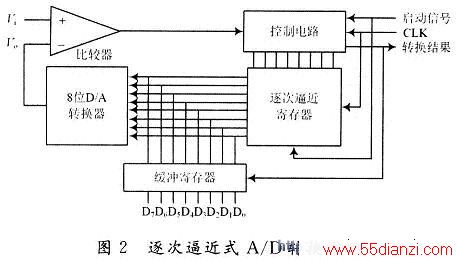

实现A/D转换的方法比较多,常见的有计数法、双积分法和逐次逼近法。由于逐次逼近式A/D转换具有速度快,分辨率高等优点,而且采用该法的ADC芯片成本较低,因此在设计中采用该种方式。逐次逼近式A/D转换器的原理如图2所示。它由逐次逼近寄存器、D/A转换器、比较器和缓冲寄存器等组成。当启动信号由高电平变为低电平时,逐次逼近寄存器清0,这时,D/A转换器输出电压V。也为O,当启动信号变为高电平时,转换开始,同时,逐次逼近寄存器进行计数。转换原理如图2所示。

逐次逼近寄存器工作时与普通计数器不同,它不是从低位向高位逐一进行计数和进位,而是从最高位开始,通过设置试探值来进行计数。在第一个时钟脉冲到来时,控制电路把最高位送到逐次逼近寄存器,使它的输出为10000000,这个输出数字一出现,D/A转换器的输出电压V。就成为满量程值的128/255。这时,若Vo>Vi则作为比较器的运算放大器的输出就成为低电平,控制电路据此清除逐次逼近寄存器中的最高位;若Vo≤Vi则比较器输出高电平,控制电路使最高位的1保留下来。

若最高位被保留下来,则逐次逼近寄存器的内容为10000000,下一个时钟脉冲使次低位D6为1。于是,逐次逼近寄存器的值为11000000,D/A转换器的输出电压Vo到达满量程值的192/255。此后,若Vo>Vi则比较器输出为低电平,从而使次高位域复位;若Vo<Vi则比较器输出为高电平,从而保留次高位为1。重复上述过程,经过N次比较以后,逐次逼近寄存器中得到的值就是转换后的数值。转换结束后,控制电路送出一个低电平作为结束信号,此信号的下降沿将逐次逼近寄存器中的数字量送入缓冲寄存器,从而得到数字量输出。

这里采用的ADC0809是单片双列直插式集成芯片,是8通道8位A/D转换器,其主要特点是:分辨率为8位;总的不可调误差±1 LSB;当模拟输入电压范围为0~5 V时,可使用单一的+5V电源;转换时间为100μs;温度范围-40~+85℃;不需另加接口逻辑可直接与CPU连接;可以输入8路模拟信号;输出带锁存器;逻辑电平与TTL兼容。

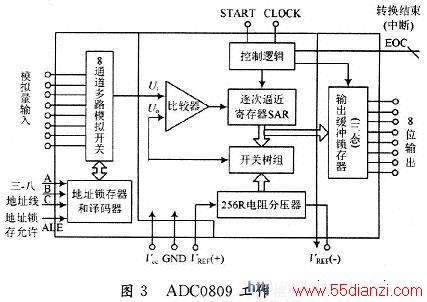

ADC0809带有8位转换器、8位多路切换开关以及与微处理机兼容的控制逻辑的CMOS组件。它的8位A/D转换器转换方法为逐次逼近法。在A/D转换器的内部,含有一个高阻抗斩波稳定比较器,一个带有模拟开关树组的256R分压器,以及一个逐次逼近的寄存器。8路的模拟开关由地址锁存器和译码器控制,可以在8个通道中任意访问一个单边的模拟信号。其工作框图如图3所示。

该A/D转换器无需调零和满量程调整。由于多路开关的地址输入能够进行锁存和译码,而且三态TTL输出也可以锁存,易于与微处理器进行接口。

如图3所示,它由两大部分所组成:第一部分是8通道多路模拟开关,它用于控制C,B,A端子和地址锁存允许端子,可使其中一个通道被选中;第二部分为一个逐次逼近型A/D转换器,它由比较器、控制逻辑、输出缓冲锁存器、逐次逼近寄存器以及开关树组和256R电阻分压器组成。后两种电路,即开关树和256R电阻分压器,组成了D/A转换器。控制逻辑用来控制逐次逼近寄存器从高位到低位逐次取1,然后将此数字量送到开关树组,即8位开关,用来控制开关S7~S0与参考电平相连接。参考电平经256R电阻分压器,输出一个模拟电压Uo,Uo,Ui在比较器中进行比较。当Uo>Ui时,本位D=O;当Uo≤Ui时,则本位D=1。因此,从D7~D0比较8次即可逐次逼近寄存器中的数字量,即与模拟量Ui所相当于的数字量相等。此数字量送入输出锁存器,并同时发转换结束脉冲。

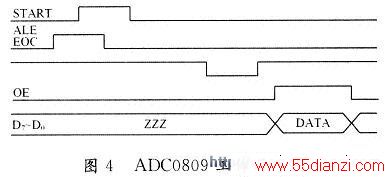

该 电压表 电路中, ADC0809 的工作时序如图4所示。主要控制信号:START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC,ADDB,ADDA)信号的锁存信号。当模拟量送至某一输入端,由3位地址信号进行选择,而地址信号由ALE锁存;EOC是档位转换的状态信号。EOC输出高电平时,表示转换结束;在EOC的上升沿后,若使能输出信号OE为高电平,则三态缓冲器打开,将转换完毕的8位数据结果输至数据总线,至此ADC0809的一次转换结束。

3.2 档位转换电路

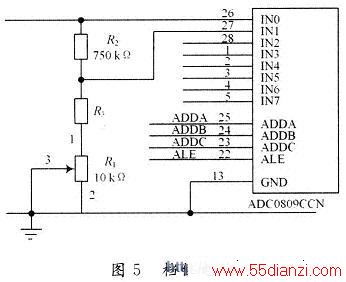

为了增加数字电压表的测量范围,设计了档位选择电路。采用精密电阻分压方法,简洁实用。ADC0809有8路数据输入端口,原理上可以分为8个档位。从实用性出发,只分了两档,如图5所示。图5中电位器负责电阻校准。尽管采用精密电阻,各电阻值的制造误差不可避免,用电位器来微调校准以保证测量精度。ADC0809的输入范围为0~5 V,档位的切换是通过程序来控制ADC0809各个通道的选通来自动实现。只要输入的电压范围超过5 V,则档位自动切换到另一档,即选通通道INl。

当输入电压范围为O~5 V时,INO导通。此时U=U26,当输入电压范围为5~50 V时, FPGA 判断选择档位,INl导通。此时有U=U27即U=(R1+R3)/(R1+R2+R3)=U26/10。

由于ADC0809数字量输出为8位,数字量化范围为0~255,当输入电压为满量程5 V时,转换电路对输入电压的分辨能力为:

![]()

本文关键字:电压表 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术