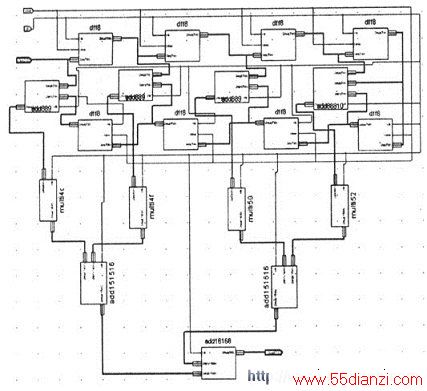

4 FIR滤波器整体电路

FIR滤波器的整体电路基本与其原理图类似。整体电路如下图所示:

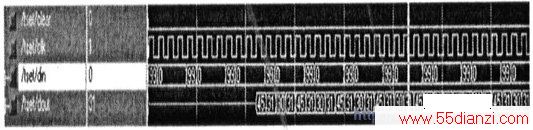

5 FIR滤波器整体电路仿真结果

当输入为信号为[99,0,0,0,99,0,0,0,99,O,0,0,99。…]滤波器的实际仿真波形见下图:

因为该滤波器为九阶,信号通过各级触发器,加发器乘法器的总延迟为13个时钟周期,故在仿真中前13个时钟周期没有信号输出。通过matl ab对滤波器进行仿真得出的理论输出序列为:[33,28,34,50,33,28,34,50,33,28,34,50,33,28,34,50…….]与实际仿真波形比较,波形基本一致,但是因为该滤波器只有九阶,所以与理论值有一定误差。

上一篇:DDS原理及基于FPGA的实现