步骤1:fscheduLED,max=min(fi,min|Ti∈Elist)

步骤2:对于F集合中的满足FMin≤f≤fscheduled,max的每个f值,计算:

选取使得计算步骤2中结果最小的,值作为FPGA的运行频率值,从而使得FPGA的总体功耗最低。

3 模拟实验及分析

由于当前并没有一个统一的基准用于评价 可重构系统 功耗相关的调度算法,因此采取了类似参考文献[2]中的模拟实验模型设计了离散时钟的模拟器,模仿实时系统中的时钟滴答以进行任务截止期的检查。然后设计随机任务生成器,生成分别含有1 000、2 000、3 009、4 000、5 000、6 000个Ti(fi,max,ωi,ai,ci,ti,ei,fworking)的任务集,硬件任务的宽度和执行时间也是随机生成的。

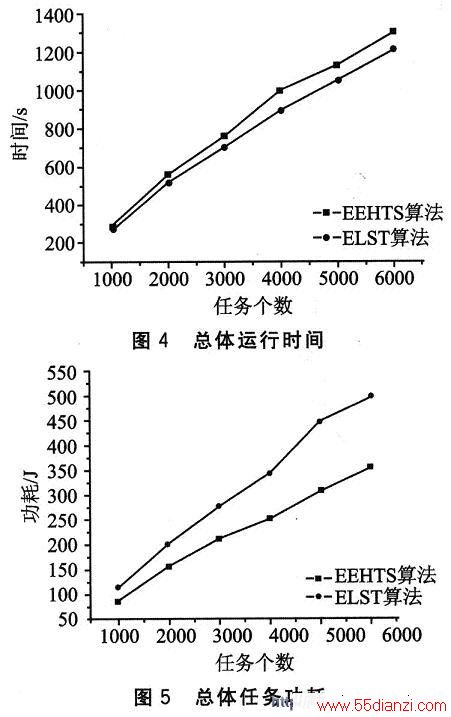

假定目标器件为Xilinx Virtex XCV1000,共96列×64行,其中可用于配置硬件任务的动态部分是80列,其他用于操作系统进行通信和I/O。模拟实验中采用的参数如下:任务的最小宽度ωmin=1,Nmax=80,任务的宽度范围ωi为1~80;fmin=20 MHz,fmax=100MHz,所以各个任务的可运行的最大频率fi,max∈[20,25,…,1 000];任务在fi,max频率时的运行时间ti范围为100~1 000 ms。ei范围为20~200 mJ,ei的大小和任务宽度相关。到达时间范围01.5~500 ms,模拟器的时钟滴答设置为500 μs。分别模拟了采用ELST算法和EEHTS算法的任务集的总体运行时间和整体功耗,如图4和图5所示。从图4中可以看到,采用ELST算法的任务运行时间曲线要比采用EEHTS算法的低,这是因为只采用ELST算法时并不改变FPGA的运行频率,FPGA始终使用最高频率运行,显然这种方法的功耗会大于EEHTS算法,实验结果也证明了这点。如图5所示,EEHTs算法虽然牺牲了一些时间性能,但是硬件任务仍然可以在其截止期内完成,并且相对于ELST算法,硬件任务功耗大约降低了32%。

结 语

在嵌入式系统中,低功耗是非常重要的目标。本文通过对可重构系统中硬件任务调度算法的研究,在对硬件任务调度时加入了对功耗的考虑,动态改变硬件任务运行的频率,从而降低系统整体功耗。

本文关键字:硬件 DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:FPGA在多串口读数系统中的应用