基于 SRAM 的 FPGA 的问世标志着现代可重构计算技术的开端,并极大地推动了其发展。可重构计算技术能够提供硬件的效率和软件的可编程性,它综合了微处理器和ASIC的特点,空间维和时间维上均可变,因而广泛应用在军事目标匹配、大数运算、声纳波束合成、基因组匹配、图像纹理填充、集成电路的计算机辅助设计等方面。对 动态可重构 相关技术的研究将推动可重构技术的发展,以满足更多的应用需求。

1 可重构体系结构

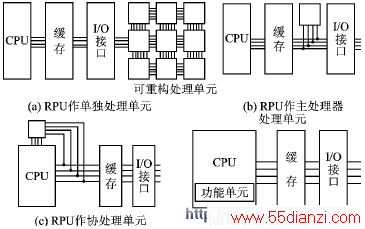

用可重构器件构造的基本体系结构,按可重构处理单元RPU和传统微处理器的耦合方式,可分为以下4种:

① 作为一个单独的处理单元通过I/O 接口连接总线,是最松散的连接方式,如图1(a)所示;

② 作为主处理器的处理单元挂在主机的本地总线上,通过Cache 来实现和主处理器之间的连接,如图1(b)所示;

③ 作为协处理单元,可以执行较大粒度的运算,如图1(c)所示;

④ RPU被集成到处理器芯片内,作为主处理器一个扩展的数据通道,提供功能可以定制的指令,如图1(d)所示。

图1 可重构单元RPU和传统微处理器的耦合关系图

2 典型动态可重构系统结构

重构可分为静态重构和动态重构。如果重构必须在中断程序执行的情况下运行,则称为“静态重构”;如果装载配置文件的过程可以与程序执行同时进行,即在改变电路功能的同时,仍然保证电路的动态接续,则称为“动态重构”。动态可重构系统多是基于多配置文件的RPU,可在运行部分配置文件的同时改变其他配置文件,从而显著缩短重新配置的时间。动态可重构技术可以使数字系统单片化的设计从追求逻辑大规模、高集成度转向追求资源利用率,从专用的固定功能逻辑系统转向功能可自适应进化的逻辑系统,其设计理论和方法已逐渐成为新的研究热点。下面介绍几种典型的动态可重构结构。

Garp: 美国加州大学伯克利分校的BRASS研究小组开发的,由一个MIPS微处理器和FPGA组合而成的系统。其核心是探索如何将可重构计算单元嵌入到传统的RISC处理器中,并论证这种可变结构对某些领域计算的加速能力。

M1、M2芯片: M1芯片是美国加州大学Morphosys工程提出的一种粗粒度、多重配置文件可重构结构;M2是M1的一种改进结构,兼具DSP器件的灵活性和ASIC 芯片的高性能,可广泛应用于并行计算系统、多媒体数据处理、高质量图像处理、DSP 变换等领域。

FIPSOC: SIDNA工程提出的一种粗粒度结构的FPGA。时序逻辑部分有多重配置文件的动态重构功能。为支持动态重构,每个寄存器中的数据都可复制,微处理器的指令和功能单元均做了改进。

DPGA: 麻省理工大学的Transit工程提出的,划分结构为二维阵列单元的DRFPGA。当DPGA器件实现时间上的重配置时,AE内部要能实现多种功能以供配置,而常规FPGA仅实现对同一功能的重复配置。

XPP(eXtreme Processing Platform) 结构: PACT公司提出的一种粗粒度实时动态可重构的数据处理技术,其中心思想是用配置流替代指令流,支持并行任务。XPP对处理大量流数据的应用效率很高,适用于无线基站、图像、视频流处理、雷达声纳、生物信息、过程仿真和加密等领域。

3 动态可重构系统的 通信结构

3.1 两种基本策略

典型的片上系统设计常常采用片上总线和片上网络两种通信策略。最常用的是片上总线,其主要优点是高灵活性,可延展,设计花销小,一般在带宽要求较低时时延也较短;缺点是过长的通信线路带来一定能耗,且限制系统时钟速率。当通信结构中含有两个以上的模块时,可伸缩性减弱。分层总线结构可以减轻关键路径上的总线负载,通过桥连接多个总线可将速度要求不同的器件隔离在不同的时钟域上,使得SoC得以延续PCB板的优良性能。

片上网络(NoC)技术从体系结构上彻底解决了总线结构所固有的三大问题:由于地址空间有限而引起的扩展性问题;由于分时通信而引起的通信效率问题;由于全局同步而引起的功耗和面积问题。其主要优点是能支持硬件模块之间的并发通信,可伸缩性更强,可用于支持更大带宽,但时延更长。元件的模块化更有利于IP重用,从而提供更高的时钟频率和低功耗。相对于总线结构使用中央控制逻辑,NoC的每个交换节点都包含缓存、路由逻辑和仲裁逻辑,因而其最大缺点是片上面积花销更大。

NoC的拓扑结构有直接网络Orthogonal拓扑、立方连接循环拓扑、Octagon拓扑等;间接网络拓扑Crossbar Switch结构、FullyConnected网络和Butterfly拓扑等。NoC拓扑方式的选择将显著影响通信架构的传输能力。为配合芯片架构复杂度与成本,芯片本身的处理特性与应用目标,在通信架构方面必须考虑拓扑的路径平均距离、可扩展大小、节点数量、顶点数量、网络直径等。由于NoC的拓扑结构选择对其产品的最终性价比起到决定性影响,因此选择正确的拓朴结构能有效缩短各种应用的设计以及验证时间。

www.55dianzi.com

3.2 通信结构

3.2.1 分类

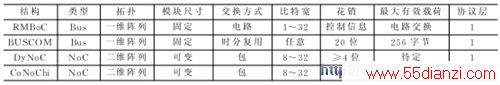

基于片上总线策略的通信结构有: RMBoC(Reconfigurable Multiple Bus on Chip)和BUSCOM。基于片上网络策略的通信结构有: DyNoC(DynamIC Network on Chip)和CoNoChi(Configurable Network on Chip) 。

RMBoC是为多处理器系统提出的,基于可重构多总线网络改进而来的。任何系统级的重构都不会改变RMBoC的模块和物理拓扑,应用层上的通信结构改变是通过层叠网上的点对点通道。该结构具有高灵活性,但是可伸缩性较弱,其结构如图2所示。

图2 RMBoC结构图

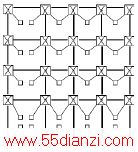

DyNoC是首个将基于包的NoC方案用于可重构设计的结构,它由处理单元和路由器组成二维阵列,每个处理单元都连接一个路由器,路由器之间相互连接。该结构的可伸缩性、延展性和可模块化性能都很好,只是灵活性欠佳。一个5×5的DyNoC系统结构图如图3所示。

图3 5×5 DyNoC系统结构图

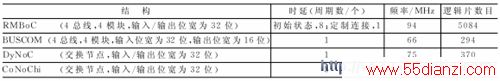

4种结构的设计参数见表1,执行参数(在VirtexII上实验得到)见表2。特别指出,片上总线的执行参数是针对整个结构,而片上网络的执行参数是针对单个交换节点。

这4种结构都能很好地满足 动态可重构 FPGA 的设计要求。片上网络的结构体现了较好的结构参数,但是片上面积花费巨大,所以当设计侧重片上效率时,首选片上总线的结构。

另外,BUSCOM只需要很少的硬件资源,而在分层总线结构中RMBoC的灵活性优于BUSCOM;CoNoChi具有最佳的结构参数,是理论上最支持动态可重构的结构,但是在VirtexII平台上执行具有一定困难,因而设计了DyNoC来适应VirtexII平台有限的可重构能力。

3.2.2 DyNoC的应用实例

交通灯控制(TLC)可以用一个3×3的DyNoC来实现,由3个模块组成: VGA控制器(VGA),交通灯视觉模块(LV)和交通灯控制模块(TC)。VGA模块可以显示目前路口情况、行人控制键和灯信号;交通灯视觉模块负责控制交通灯内部构造,由VGA模块显示;交通灯控制模块(TC)用来获取行人需求。VGA发出X和Y 像素扫描的位置给交通灯视觉模块,并接收需要显示的颜色;FSM模块用来监控行人的键控输入(片上有两个按钮),向交通灯视觉模块发送转换灯状态的信息,然后显示相应颜色的灯。在3×3 DyNoC中,用正中的路由器来实现与其他所有路由器的连接,其他路由器也保持相互通信以确保高通信量。整个交通灯控制(TLC)的实现可以在没有中断和故障的情况下运行。

表1 4种结构的设计参数

表2 执行参数(在VirtexII上实验得到)

4 相关问题和发展趋势

① 目前片上系统设计中各IP组件可重用,但通信结构无法重用。因此在系统重构时,怎样为动态配置的模块提供一个灵活快速的通信接口成为主要问题。可研究一种动态可重构的NoC架构,能为各IP之间的通信提供灵活的接口,并能通过片上引脚与板级系统的其他芯片进行数据交换,提供较好的通信质量QoS,包括高吞吐量和短延迟等。