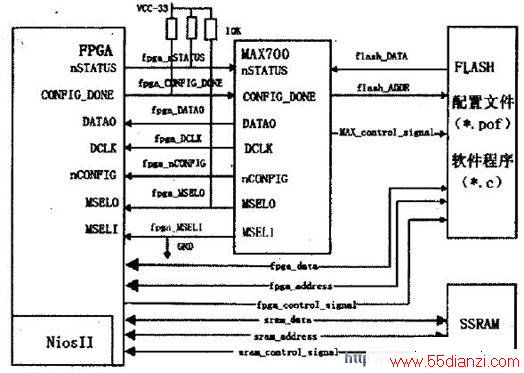

嵌入式系统中FPGA 的PS方式配置方式电路设计如图3所示。FPGA和FLASH、SSRAM组成了一个最基本的嵌入式系统,其中将Nios II软核处理器嵌入到FPGA中。FLASH 作为程序的存储器,其中存储着系统的整个软件应用程序和配置文件。SSAM作为系统程序运行空间,可以有效地解决配置控制器自身SRAM容量小的问题。

图3 PS方式配置方式电路设计

在图3所示的设计中,MSEL0和MSEL1是配置专用线,如果MSEL0接高电平(VCC),MSEL1接地(GND),则此时的配置模式为PS模式; 如果MSELO 和MSEL1都接地(GND),则配置模式为AS模式。CPLD控制器的控制信号MAX_control_signal主要包括flash_CS_n (片选)、flash_OE_n (输出使能)、flash_RW_n (读写使能)、flash_RESET_n(重置)、flash_BYTE_n (字节传输)等信号线。

配置文件通过ALTEra的Quartus II软件以.pof(Programmer Object Files)文件格式下载到EPM7256配置控制器内,如果配置有错误,该配置控制器可以进行多次下载,直至最终完成配置功能。

FLASH中存储的程序包括系统配置程序文件、软件程序,其格式为.flash。系统加电后,配置控制器从FLASH 的0地址开始将配置文件进行并/串转换后(即将图3中的flash_DATA[7..0]转换为DATA0)加载到FPGA中,完成系统加电时的自动配置功能;同时Nios II处理器将FLASH 中的应用程序移至到SSRAM 中运行,从而实现嵌入式系统的初运行。通过Nios II IDE工具可以将配置文件FPGA 的.SOF文件格式转换为Flash存储器所需要的. flash文件格式。

4 配置文件的设计与实现

为了确保配置过程的正确,提高系统的配置性能,在配置文件设计时应严格按照FPGA的Ps配置流程进行,并在配置过程中始终监控配置工作状态,在完善的配置程序配合下可以纠正如上电次序导致配置不正常等错误。该配置程序是采用VHDL语言编写的,编写完成后,将配置文通过JTAG接口下载到EPM7256配置控制器内,根据图2的PS配置时序,其配置流程如下:

(1)配置信号的初始化:DATAO=0,DCLK=0,nCONFIG=0,CONF_DONE=1和nSTATUS=1,并保持2 us以上。

(2)检测nSTATUS,如果为“0”,表明FPGA 已响应配置,可开始进行配置,否则报错,并返回1。正常情况下,nCONFIG=0后1 us内nSTATUS为“0”。

(3)置nCONFIG=1,并延时5 us。

(4)DATAO上放置数据(低位在前),DCLK=1,延时。

(5)DCLK=0,并检测nSTATUS,若为“0”,则报错,重返1。

(6)准备下一位数据,并重新执行(4)、(5),直到数据发送完为止。

(7)此时CONF_DONE应变成“1”,表明FPGA已完成配置,如果数据发送完后,CONF_DONE为“0”,必须重新配置返回1。

(8)配置完成后,再送出299个周期(Cyclone要求的)的DCLK,以便FPGA完成初始化。

5 结束语

本文介绍了通过用CPLD 的MAX7000 系列配置控制器EPM7256和Flash实现Cyclone系列的EP1C6Q240C8 FPGA配置文件下载更新的方法。与传统的JTAG或PROM 串行下载配置方法相比,此方法具有更新配置文件灵活方便、易于操作、更加有利于系统配置文件的升级等特点。与常用的串行配置方法相比,该配置方法更具有配置时间短,准确率高、易于实现等优点。虽然该配置控制电路是为配置Altera公司cyclone系列的FPGA器件而设计的,但稍加修改也适用于其它系列的。FPGA器件,故其有一定的通用性,采用此方法特别适用于需要不断更新的系统设计中,具有较为广阔的应用前景。