通过以上对ATmega64单片机寻址空间的扩展方法,可以实现ATmega64单片机对合适的Flash存储器的寻址操作,从而解决了大容量FPGA配置数据的存储和读取问题。

2.2.3 用ATmega64实现FPGA的SELECTMAP加载

Xilinx公司的Spartan3系列FPGA加载方式分为5种: Master Serial、Slave Serial、Master Parallel、Slave Parallel、JTAG。

按照FPGA是否控制加载过程,加载方式可分为Master方式和Slave方式;按照加载数据时的数据位宽,可分为Serial方式和Parallel方式。用于加载的引脚主要有:PROG_B,CCLK,RDWR_B,DONE,INIT_B,CS_B,BUSY,D[0~7],M[0~2],HSWAP和JTAG接口(TDI、TMS、TCK、TDO)。加载过程大体分为3个步骤:配置的建立、配置数据的加载和加载完成。

SELECTMAP即Slave Parallel方式,是由外部控制器控制FPGA的加载过程,并以8位数据的形式向FPGA写入加载数据的加载方法。图2中FPGA与ATmega64的连接部分为ATmega64单片机采用SELECTMAP方式对FPGA进行加载的硬件连接框图,具体实现过程如下:

ATmega64通过将FPGA的PROG_B、CS_B和RDWR_B引脚置低来开启加载过程,FPGA在PROG_B置低后开始清除内部配置RAM,并将INIT_B脚置低。PROG_B重新置1后,在INIT_B由低变高的上升沿,FPGA采样M[0~2]引脚获取配置方式信息。ATmega64监视FPGA的INIT_B脚,当INIT_B脚由低变高时,说明FPGA已经完成了内部配置RAM的清除工作,并准备好接收配置数据。在ATmega64给出的CCLK配置时钟的上升沿,配置数据D[0~7]写入配置RAM。当FPGA接收完所有的配置数据后,DONE引脚被FPGA置为高电平。ATmega64可以通过监视DONE引脚来判断FPGA是否加载完成。对于Spartan3系列的FPGA,如果配置FPGA的CCLK的频率高于50MHz,则外部控制器还需要监视FPGA的BUSY引脚。当BUSY脚为高时,说明FPGA还未完成上一个配置数据的处理,此时外部控制器需要继续保持上一个配置数据在D[0~7]引脚,直至BUSY引脚回到低电平。对于本设计的应用,ATmega64给出的配置时钟频率远低于50MHz,不必考虑BUSY引脚的控制作用。

3 软件设计

3.1 主控计算机的软件设计

主控制计算机的软件运行状态应该分为两种:一是平时的查询控制状态,用来查询和控制系统中各个节点的工作状态;二是系统的升级状态,用来执行对各个子节点的升级控制。如图4所示,这两种状态是可以相互转换的。

![]()

图4 主控计算机主要状态

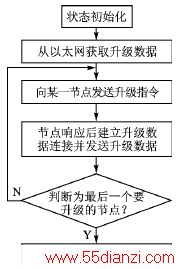

软件的查询控制状态,是由系统所要实现的主要功能决定的,不属于本文所讨论的范畴。在系统的升级状态,主控计算机先要通过以太网获得系统各个节点的 远程升级 数据,待全部升级数据接收完成后,向系统的一个节点发送升级指令。节点响应并建立起通信连接后,将该节点的升级数据全部发送到该节点。接下来,主控计算机判断上一个节点是否为最后一个需要升级的节点,如果不是,则继续进行下一个节点升级数据的传输。系统所有的节点升级完成后,等待外部输入的控制命令。例如,让整个系统重新启动,加载新的数据;或暂时不重新启动而返回查询控制状态。软件流程如图5所示。

图5 系统升级状态流程

3.2 子节点的软件设计

对于子节点的软件设计,与主控计算机一样,也分为平时的查询控制状态和系统升级状态,并且它们之间也能够与主控计算机一起相互转换;但 ATmega64 单片机还要承担对 FPGA 的加载任务。开机运行后,ATmega64单片机先加载子节点FPGA,使子节点能够正常工作。子节点正常工作后,监视RS485总线并判断有无对本节点的通信。当主控计算机要求与本节点建立通信连接时,发送反馈信息,与其建立通信连接。子节点根据主控计算机发送的命令,进入查询控制模式或者远程升级模式。进入远程升级模式后,子节点接收主控计算机发来的远程升级数据,升级数据经过校验后写入Flash。升级完成后继续等待主控计算机的命令,重新启动或继续运行。其具体的软件设计流程如图6所示。

图6 子节点软件流程

结语

FPGA既继承了ASIC的大规模、高集成度、高可靠性的优点,又克服了普通ASIC周期长、投资大、灵活性差的缺点,逐步成为许多系统实现的理想选择。特别是随着FPGA容量和性能的提升,加上其独特的硬件升级能力,其应用范围越来越广。本文所提出的对大容量FPGA构成的多节点系统的远程升级方法,系统构成简单、技术成熟,而且具有明显的成本优势。

参考文献

[1] 宓城,徐新民.利用GPRS网络对FPGA系统进行远程更新[J]. 电子技术, 2005(6):24-26.

[2] Atmel. ATmega64 Data Sheet,200503.

[3] Xilinx. Spartan3 Complete Data Sheet,200501.

[4] 廖传书,程鑫.基于GPRS的配电网远程监控终端的设计[J]. 电子技术应用, 2007,33(5):8082.

本文关键字:暂无联系方式DSP/FPGA技术,单片机-工控设备 - DSP/FPGA技术

上一篇:移动操作SoC接口IP组件设计